Un artículo de investigación recientemente publicado describe un chip de computación en memoria (CIM) que combina neuronas artificiales con RAM resistiva (RRAM) para que los pesos del modelo de IA puedan almacenarse y procesarse en el mismo chip.

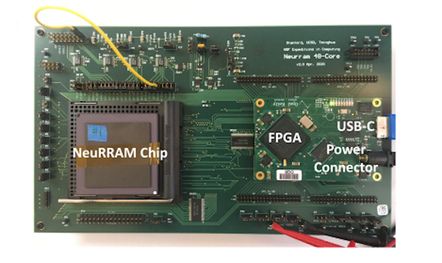

Un chip de computación en memoria basado en memoria resistiva de acceso aleatorio (haga clic para ampliar). Imagen: Wan et al.

Los investigadores detrás del diseño afirman que sería más eficiente para aplicaciones perimetrales porque elimina el movimiento de datos entre bloques de cómputo y memoria separados.

La informática perimetral y la inteligencia artificial están en camino de un crecimiento meteórico en el futuro cercano, al menos según la empresa analista IDC. Algunos escenarios los combinan porque las implementaciones perimetrales pueden estar limitadas en cuanto a energía y conectividad, pero aun así necesitan analizar volúmenes significativos de datos y brindar una respuesta casi en tiempo real a los eventos, lo que hace que un modelo de IA "viva" en el dispositivo sea la solución más óptima. .

A la luz de esto, un grupo de investigadores ha desarrollado un chip que llama NeuRRAM, porque combina neuronas artificiales con RRAM en una arquitectura novedosa. El objetivo del proyecto era ofrecer un diseño que pudiera ofrecer simultáneamente una alta eficiencia energética, así como la versatilidad para admitir varios modelos de IA y una precisión comparable a ejecutar el mismo modelo en el software.

El proyecto comenzó inicialmente como parte de un proyecto de Nature Science Foundation llamado "Expediciones en Computación". Este proyecto reunió a un grupo de investigadores de diferentes instituciones con diferentes antecedentes, incluidos algunos de Stanford y UCSD, así como investigadores de la Universidad de Tsinghua en China que son expertos en la fabricación de dispositivos RRAM.

Eficiencia energética: inferencia de IA realizada en el artilugio alimentado por batería

Según Weier Wan, investigador graduado de la Universidad de Stanford y uno de los autores del artículo, publicado ayer en Nature, NeuRRAM se ha desarrollado como un chip de IA que mejora en gran medida la eficiencia energética de la inferencia de IA, lo que permite que las funciones complejas de IA se realicen directamente dentro de dispositivos de borde alimentados por batería, como dispositivos portátiles inteligentes, drones y sensores industriales de IoT. .

“En los chips de IA actuales, el procesamiento y el almacenamiento de datos se realizan en lugares separados: la unidad de cómputo y la unidad de memoria. El movimiento frecuente de datos entre estas unidades consume la mayor parte de la energía y se convierte en el cuello de botella para la realización de procesadores de inteligencia artificial de bajo consumo para dispositivos periféricos”, dijo.

Para abordar esto, el chip NeuRRAM implementa un modelo de "cómputo en memoria", donde el procesamiento ocurre directamente dentro de la memoria. También utiliza RAM resistiva (RRAM), un tipo de memoria que es tan rápida como la RAM estática pero no volátil, lo que le permite almacenar pesos de modelos de IA. Una característica clave de las celdas RRAM es que los pesos neuronales pueden almacenarse en celdas de memoria como diferentes niveles de conductancia, codificarse a través de convertidores de digital a analógico (DAC) y alimentarse a la matriz de memoria.

Esto no es una simulación de software, es hardware.

Ha habido estudios previos sobre arquitecturas CIM, pero este es el primero en demostrar una amplia gama de aplicaciones de IA en simulación de hardware en lugar de software, mientras que es más eficiente energéticamente y capaz de ejecutar los algoritmos con precisión, algo que ninguno de los estudios anteriores pudieron mostrarse simultáneamente, según Wan.

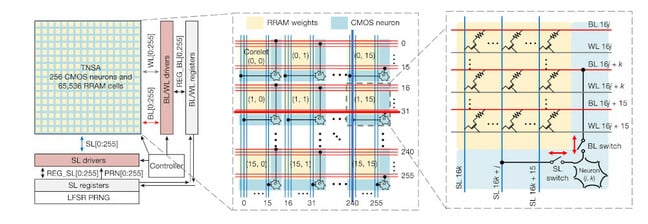

La NeuRRAM consta de 48 núcleos CIM que comprenden un total de 3 millones de celdas RRAM. Cada núcleo se describe como una matriz neurosináptica transponible (TNSA) que consta de una cuadrícula de 256 × 256 células RRAM y 256 circuitos de neuronas artificiales CMOS que implementan convertidores de analógico a digital (ADC) y funciones de activación.

Según el documento, la arquitectura TNSA se diseñó para ofrecer un control flexible de la dirección de los flujos de datos, lo cual es crucial para admitir una amplia gama de modelos de IA con diferentes patrones de flujo de datos.

Por ejemplo, en las redes neuronales convolucionales (CNN) que son comunes en tareas relacionadas con la visión, los datos fluyen en una sola dirección a través de capas para generar representaciones de datos en diferentes niveles de abstracción, mientras que en algunos otros modelos el muestreo probabilístico se realiza de un lado a otro entre capas. hasta que la red converja a un estado de alta probabilidad.

Sin embargo, otros diseños que combinaron CIM con RRAM se limitaron a operar en una sola dirección, generalmente conectando filas y columnas de la matriz de barras transversales RRAM a circuitos dedicados en la periferia para controlar las entradas y medir las salidas, dice el documento.

Cómo funciona

El secreto de la reconfigurabilidad de NeuRRAM es que distribuye los circuitos neuronales CMOS entre las células RRAM y las conecta a lo largo de filas y columnas.

Cada TNSA se divide en una serie de corelets, cada uno de los cuales consta de 16 × 16 células RRAM y un circuito de neuronas. Los corelets están conectados por líneas de bits compartidas (BL) y líneas de palabra (WL) a lo largo de la dirección horizontal, y líneas de fuente (SL) a lo largo de la dirección vertical.

El circuito de la neurona se conecta a través de interruptores a un BL y un SL de los 16 de cada uno que pasa por el corelet, y es responsable de integrar las entradas de todas las 256 RRAM que se conectan al mismo BL o SL.

Cada circuito neuronal puede usar sus interruptores BL y SL para entrada y salida. Esto significa que puede recibir la multiplicación matriz-vector analógica (MVM) de una celda RRAM procedente de BL o SL a través de los conmutadores, pero también puede enviar los resultados digitales convertidos a registros periféricos a través de los mismos conmutadores.

Esta disposición significa que se pueden implementar diferentes direcciones de flujo de datos configurando qué interruptor usar durante las etapas de entrada y salida de cada circuito neuronal.

(Esta arquitectura también nos recuerda un poco a Chip procesador de IA de SambaNova, que se implementa como una cuadrícula de unidades de cómputo y unidades de memoria, unidas por un tejido de comunicación en el chip que controla el flujo de datos).

Para maximizar el rendimiento de la inferencia de IA utilizando los 48 núcleos CIM en NeuRRAM, es posible implementar varias estrategias de asignación de peso que explotan tanto el paralelismo del modelo como el paralelismo de los datos, según el artículo.

En el caso de una CNN, la estrategia podría ser duplicar los pesos de las primeras capas más intensivas desde el punto de vista computacional en múltiples núcleos CIM para la inferencia paralela. El documento proporciona una descripción más detallada de las estrategias de mapeo de peso disponibles.

El documento informa resultados de inferencia medidos por hardware utilizando el chip para una variedad de tareas de IA, incluidas clasificaciones de imágenes utilizando conjuntos de datos CIFAR-10 y MNIST, reconocimiento de comandos de voz de Google y recuperación de imágenes MNIST, implementados con varios modelos de IA.

Se afirma que logra una precisión de inferencia comparable a los modelos de software entrenados con pesos de 4 bits en todas estas tareas de referencia. Por ejemplo, logra una tasa de error del 0.98 % en el reconocimiento de dígitos escritos a mano del MNIST con una CNN de 7 capas, una tasa de error del 14.34 % en la clasificación de objetos CIFAR-10 con ResNet-20 y una tasa de error del 15.34 % en el reconocimiento de comandos de voz de Google con una LSTM de 4 celdas (memoria larga a corto plazo).

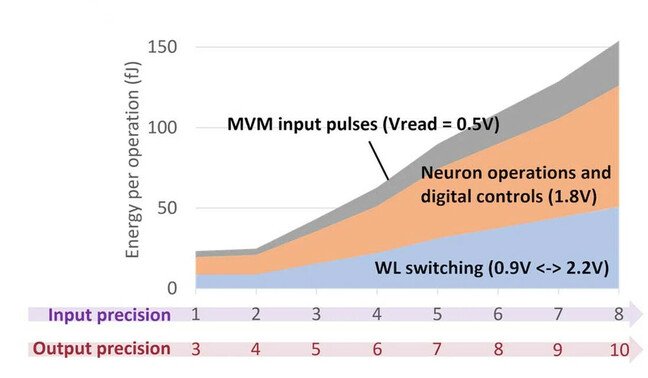

También se afirma que el chip NeuRRAM tiene una eficiencia energética dos veces mejor que los diseños de chips CIM anteriores que utilizan RRAM, en varias precisiones de bits computacionales. Sin embargo, el consumo de energía en el documento no se cita en una forma que sea fácil de comparar con los dispositivos comerciales en el mercado, y la figura que se muestra a continuación ilustra el consumo de energía por operación en diferentes precisiones de bit medidas en femtojulios (fJ).

Sin embargo, Wan nos dijo que para una tarea típica de detección de palabras clave en tiempo real que se ejecuta en muchos dispositivos domésticos inteligentes hoy en día (como decirle a un altavoz inteligente que encienda la luz), se estima que NeuRRAM consume menos de 2 microvatios de energía.

“Eso significa que incluso con una pequeña batería de moneda, podría funcionar durante más de 10 años (sin considerar la energía consumida por otros componentes del sistema)”, dijo.

Según el documento, el chip se fabrica utilizando una tecnología CMOS de 130 nm, y se espera que la eficiencia energética mejore con la escala de la tecnología, como es el caso de otros productos semiconductores.

La productización aún está a años de distancia

Entonces, ¿veremos un dispositivo comercial de envío basado en esta tecnología? Wan dice que tiene un gran potencial para ser comercializado y personalmente está considerando trabajar en producirlo él mismo.

"Es muy probable que el caso de uso inicial más adecuado sea extremo / IoT", nos dijo.

Un producto basado en el chip NeuRRAM podría combinarse en un sistema con una CPU, como con otros aceleradores, pero esto no es necesario para todas las aplicaciones.

“Recientemente ha habido una tendencia de que los datos de los sensores se envíen directamente a los procesadores de IA sin pasar por la CPU o la memoria adicional”, dijo Wan, pero agregó que para la mayoría de los casos de implementación en el mundo real, estos aceleradores de IA funcionan como un coprocesador. para una CPU, donde la CPU administra otras tareas.

El chip NeuRRAM está diseñado solo para trabajos de inferencia, en gran parte porque la tecnología RRAM en su forma actual no es muy adecuada para el entrenamiento porque el proceso de entrenamiento requiere actualizaciones frecuentes de la memoria, y esta es "una operación muy costosa en RRAM", dijo Wan.

“Actualmente, muchas fundiciones comerciales ya tienen la capacidad de fabricar dispositivos RRAM, pero principalmente para usos de memoria integrada en lugar de computación en memoria. Una vez que el proceso RRAM esté más disponible para los diseñadores de circuitos integrados, podría surgir un producto NeuRRAM”.

Sin embargo, es difícil predecir el cronograma exacto para que esto suceda, y Wan dijo que podría ser en los próximos dos o tres años, o mucho más. ®

- AI

- arte ai

- generador de arte ai

- robot ai

- inteligencia artificial

- certificación de inteligencia artificial

- inteligencia artificial en banca

- robots de inteligencia artificial

- robots de inteligencia artificial

- software de inteligencia artificial

- blockchain

- conferencia blockchain ai

- Coingenius

- inteligencia artificial conversacional

- criptoconferencia ai

- de dall

- deep learning

- google ai

- máquina de aprendizaje

- Platón

- platón ai

- Inteligencia de datos de Platón

- Juego de Platón

- PlatónDatos

- juego de platos

- escala ia

- sintaxis

- El registro

- zephyrnet