Aquí está el BWAIN de esta semana, nuestro término jocoso para un Error con un nombre impresionante.

BWAIN es un galardón que otorgamos cuando una nueva falla de ciberseguridad no solo resulta interesante e importante, sino que también aparece con su propio logotipo, nombre de dominio y sitio web.

Este está doblado Fuga ÆPIC, un juego de palabras APIC y EPIC.

El primero es la abreviatura de Controlador de interrupción programable avanzado, y este último es simplemente la palabra "épica", como en gigante, masivo, extremo, Mega, enorme.

La letra Æ no se ha utilizado en inglés escrito desde la época de los sajones. Su nombre es aescpronunciado ceniza (como en el árbol), y representa más o menos el sonido de la A en la palabra moderna ASH. Pero asumimos que se supone que debes pronunciar la palabra ÆPIC aquí como “APIC-slash-EPIC”, o como “ah!-eh?-PIC”.

¿De que trata todo esto?

Todo esto plantea cinco preguntas fascinantes:

- ¿Qué es un APIC?, y ¿por qué lo necesito?

- ¿Cómo puedes tener datos que incluso el núcleo no se puede mirar?

- ¿Qué causa este fracaso épico? en APIC?

- ¿Tiene el Fuga ÆPIC me afecta?

- Qué hacer al respecto?

¿Qué es un APIC?

Retrocedamos hasta 1981, cuando apareció por primera vez la PC de IBM.

La PC incluía un chip llamado Controlador de interrupción programable Intel 8259A, o foto. (Los modelos posteriores, desde PC AT en adelante, tenían dos PIC, encadenados, para admitir más eventos de interrupción).

El propósito del PIC era, literalmente, interrumpir el programa que se ejecutaba en el procesador central (CPU) de la PC cada vez que ocurría algo urgente que requería atención inmediata.

Estas interrupciones de hardware incluían eventos como: el teclado recibiendo una pulsación de tecla; el puerto serie recibiendo un caracter; y un temporizador de hardware que se repite.

Sin un sistema de interrupción de hardware de este tipo, el sistema operativo tendría que estar plagado de llamadas de función para verificar las pulsaciones de teclas entrantes de forma regular, lo que sería una pérdida de potencia de la CPU cuando nadie estuviera escribiendo, pero no respondería. suficiente cuando lo hicieron.

Como puede imaginar, al PIC pronto le siguió un chip mejorado llamado APIC, un avanzado una especie de PIC integrado en la propia CPU.

En estos días, los APIC brindan mucho más que solo comentarios del teclado, el puerto serie y el temporizador del sistema.

Los eventos APIC se activan (y proporcionan datos en tiempo real sobre) eventos como el sobrecalentamiento y permiten la interacción del hardware entre los diferentes núcleos en los procesadores multinúcleo contemporáneos.

Y los chips Intel de hoy, si se nos permite simplificar mucho, generalmente se pueden configurar para que funcionen de dos maneras diferentes, conocidas como modo xAPIC y Modo x2APIC.

Aquí, xAPIC es la forma "heredada" de extraer datos del controlador de interrupciones, y x2APIC es la forma más moderna.

Simplificando aún más, xAPIC se basa en lo que se llama MIO, corto para entrada/salida mapeada en memoria, para leer datos del APIC cuando registra un evento de interés.

En el modo MMIO, puede averiguar qué desencadenó un evento APIC leyendo desde una región específica de la memoria (RAM), que refleja los registros de entrada/salida del propio chip APIC.

Estos datos xAPIC se asignan a un bloque de memoria de 4096 bytes en algún lugar de la memoria RAM física de la computadora.

Esto simplifica el acceso a los datos, pero requiere una interacción molesta, compleja (y, como veremos, potencialmente peligrosa) entre el chip APIC y la memoria del sistema.

Por el contrario, x2APIC requiere que usted leer los datos APIC directamente del propio chip, utilizando lo que se conoce como Registros específicos del modelo (MSR).

Según Intel, evitar la parte MMIO del proceso “proporciona una capacidad de direccionamiento del procesador significativamente mayor y algunas mejoras en la entrega de interrupciones”.

En particular, extraer los datos APIC directamente de los registros en el chip significa que la cantidad total de datos admitidos y la cantidad máxima de núcleos de CPU que se pueden administrar al mismo tiempo no se limita a los 4096 bytes disponibles en el modo MMIO.

¿Cómo puede tener datos que ni siquiera el núcleo puede ver?

Probablemente ya haya adivinado que los datos que terminan en el área de memoria MMIO cuando usa el modo xAPIC no siempre se administran con el cuidado que debería...

…y por lo tanto, algún tipo de “fuga de datos” en esa área MMIO es el corazón de este problema.

Pero dado que tu ya necesita poderes de nivel de administrador de sistemas para leer los datos MMIO en primer lugar y, por lo tanto, casi con certeza podría obtener todos y cada uno de los datos en la memoria de todos modos...

…por qué el hecho de que los datos de otras personas aparezcan por error en el área de datos de APIC MMIO representa una EPIC ¿fuga?

Podría hacer que algunos tipos de ataques de robo de datos o raspado de RAM sean un poco más fáciles en la práctica, pero seguramente no le daría más capacidad de husmear en la memoria de la que ya tenía en teoría.

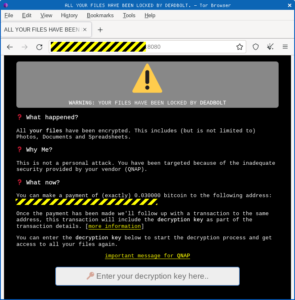

Desafortunadamente, esa suposición no es cierta si algún software en el sistema usa Intel SGX, abreviatura de Extensiones de protección de software.

MÁS INFORMACIÓN SOBRE SGX

SGX es compatible con muchas CPU Intel recientes y proporciona una manera para que el kernel del sistema operativo "selle" una porción de código y datos en un bloque físico de RAM para formar lo que se conoce como un enclave.

Esto hace que se comporte, al menos temporalmente, de forma muy parecida a los chips de seguridad especiales de los teléfonos móviles que se utilizan para almacenar secretos, como las claves de descifrado.

Una vez que se establece el "bloqueo" SGX del enclave, solo el código del programa que se ejecuta dentro del área de memoria sellada puede leer y escribir el contenido de esa RAM.

Como resultado, los detalles internos de cualquier cálculo que ocurra después de que se active el enclave son invisibles para cualquier otro código, subproceso, proceso o usuario en el sistema.

Incluyendo el kernel en sí.

Hay una forma de llamar al código que ha sido sellado en el enclave, y una forma de devolver el resultado de los cálculos que podría realizar, pero no hay forma de recuperar, espiar o depurar el código y sus datos asociados mientras se ejecuta.

El enclave se convierte efectivamente en una caja negra a la que puede enviar entradas, como datos para firmar con una clave privada, y extraer salidas, como la firma digital generada, pero de la que no puede sacar las claves criptográficas. utilizado en el proceso de firma.

Como puede imaginar, si los datos que se supone que deben estar sellados dentro de un enclave SGX se duplican accidentalmente en la RAM MMIO que se usa para "reflejar" los datos APIC cuando usa el modo xAPIC "asignado en memoria"...

…eso violaría la seguridad de SGX, que dice que ningún dato debe emerger de un enclave SGX después de que se haya creado, a menos que sea exportado deliberadamente por el código que ya se ejecuta dentro del propio enclave.

¿Qué causa esta falla épica en APIC?

Los investigadores detrás de la Papel de fugas ÆPIC descubrió que al organizar la lectura de datos APIC a través de una secuencia astuta e inusual de accesos a la memoria...

…podrían engañar al procesador para que llene el espacio APIC MMIO no solo con datos recién recibidos del propio APIC, sino también con datos que la CPU utilizó recientemente para algún otro propósito.

Este comportamiento es un efecto secundario del hecho de que, aunque la página de memoria APIC MMIO tiene un tamaño de 4096 bytes, el chip APIC en modo xAPIC en realidad no produce 4096 bytes de datos y la CPU no siempre neutraliza correctamente las partes no utilizadas de la región MMIO llenándola primero con ceros.

En cambio, los datos antiguos que quedaban en la memoria caché de la CPU se escribieron junto con los nuevos datos recibidos del propio chip APIC.

Como lo expresaron los investigadores, el error se reduce a lo que se conoce como lectura de memoria no inicializada, en el que accidentalmente reutiliza los datos sobrantes de otra persona en la RAM porque ni ellos ni usted la vaciaron de sus secretos anteriores primero.

¿Me afecta la Fuga de ÆPIC?

Para obtener una lista completa de los chips afectados, consulte Asesoramiento propio de Intel.

Por lo que podemos decir, si tiene un procesador Intel de décima u undécima generación, probablemente se vea afectado.

Pero si tiene una CPU de 12.ª generación completamente nueva (la más reciente en el momento de escribir este artículo), parece que solo los chips de clase de servidor se ven afectados.

Irónicamente, en los chips para portátiles de 12.ª generación, Intel ha renunciado a SGX, por lo que este error no se aplica porque es imposible tener enclaves SGX "sellados" que puedan filtrarse.

Por supuesto, incluso en un chip potencialmente vulnerable, si no confía en ningún software que use SGX, entonces el error tampoco se aplica.

Y el bicho, apodado CVE-2022-21233, solo puede ser explotado por un atacante que ya tenga acceso local a nivel de administrador (raíz) a su computadora.

Usuarios habituales no puede acceder al bloque de datos APIC MMIO y, por lo tanto, no tiene forma de echar un vistazo a nada allí, y mucho menos a los datos secretos que podrían haberse filtrado de un enclave SGX.

También, máquinas virtuales invitadas (VM) que se ejecutan bajo el control de un sistema operativo host en un hipervisor como HyperV, VMWare o VirtualBox casi con certeza no pueden usar este truco para robar secretos de otros invitados o del propio host.

Esto se debe a que las máquinas virtuales invitadas generalmente no tienen acceso al circuito APIC real en el procesador host; en su lugar, cada invitado obtiene su propio APIC simulado que es único para esa máquina virtual.

¿Qué hacer?

No entre en pánico.

En una computadora portátil o de escritorio, es posible que no corra ningún riesgo, ya sea porque tiene una computadora más antigua (¡o, por suerte, una nueva!) o porque no confía en SGX de todos modos.

E incluso si está en riesgo, cualquiera que ingrese a su computadora portátil como administrador/raíz probablemente ya tenga suficiente poder para causarle un mundo de problemas.

Si tiene servidores vulnerables y confía en SGX como parte de su seguridad operativa, consulte el aviso de seguridad de Intel INTEL-SA-00657 para obtener información sobre protección y mitigación.

Según los investigadores que escribieron esto, "Intel [ha] lanzado microcódigo y actualizaciones del kit de desarrollo de software SGX para solucionar el problema".

El equipo del kernel de Linux también parece estar trabajando en este momento en un parche que le permitirá configurar su sistema para que siempre use x2APIC (que, como recordará anteriormente, no transmite datos APIC a través de la memoria compartida), y evitará con gracia que el sistema vuelva al modo xAPIC después del arranque.

- APIC

- Fuga ÆPIC

- blockchain

- Coingenius

- carteras de criptomonedas

- intercambio crypto

- criptografía

- CVE-2022-21233

- seguridad cibernética

- ciberdelincuentes

- La Ciberseguridad

- De pérdida de datos

- departamento de seguridad nacional

- billeteras digitales

- EPIC

- cortafuegos

- Kaspersky

- el malware

- Mcafee

- Seguridad desnuda

- NexBLOC

- Platón

- platón ai

- Inteligencia de datos de Platón

- Juego de Platón

- PlatónDatos

- juego de platos

- SGX

- VPN

- vulnerabilidad

- seguridad del sitio web

- zephyrnet

![T3 Ep111: El riesgo comercial de un sórdido "desfiltrador de desnudos" [Audio + Texto] T3 Ep111: El riesgo empresarial de un sórdido “desnudo sin filtro” [Audio + Texto] PlatoBlockchain Data Intelligence. Búsqueda vertical. Ai.](https://platoblockchain.com/wp-content/uploads/2022/08/bn-1200-2-300x157.png)

![T3 Ep93: Seguridad en la oficina, costos de infracciones y parches tranquilos [Audio + Texto] T3 Ep93: Seguridad de la oficina, costos de infracciones y parches tranquilos [Audio + Texto] Inteligencia de datos de PlatoBlockchain. Búsqueda vertical. Ai.](https://platoblockchain.com/wp-content/uploads/2022/07/s3-ep93-1200-300x157.png)

![T3 Ep124: Cuando las llamadas aplicaciones de seguridad se vuelven deshonestas [Audio + Texto] T3 Ep124: Cuando las llamadas aplicaciones de seguridad se vuelven deshonestas [Audio + Texto]](https://platoblockchain.com/wp-content/uploads/2023/03/s3-ep124-when-so-called-security-apps-go-rogue-audio-text-300x157.png)