Un article de recherche récemment publié décrit une puce de calcul en mémoire (CIM) qui combine des neurones artificiels avec une RAM résistive (RRAM) afin que les poids du modèle d'IA puissent être stockés et traités sur la même puce.

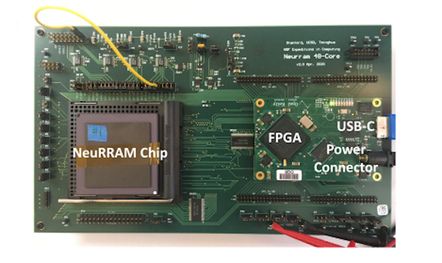

Une puce de calcul en mémoire basée sur une mémoire résistive à accès aléatoire (cliquez pour agrandir). Image : Wan et al

Les chercheurs à l'origine de la conception affirment qu'elle serait plus efficace pour les applications de pointe car elle élimine le mouvement des données entre des blocs de calcul et de mémoire séparés.

L'informatique de pointe et l'intelligence artificielle sont toutes deux sur la voie d'une croissance fulgurante dans un avenir proche, du moins selon la société d'analyse IDC. Certains scénarios les combinent car les déploiements en périphérie peuvent être limités en termes de puissance et de connectivité, mais doivent encore analyser des volumes importants de données et fournir une réponse en temps quasi réel aux événements, faisant d'un modèle d'IA "vivant" dans l'appareil la solution la plus optimale. .

À la lumière de cela, un groupe de chercheurs a développé une puce qu'il appelle NeuRRAM, car elle combine des neurones artificiels avec de la RRAM dans une nouvelle architecture. L'objectif du projet était de fournir une conception capable de fournir simultanément une efficacité énergétique élevée ainsi que la polyvalence nécessaire pour prendre en charge divers modèles d'IA, et une précision comparable à l'exécution du même modèle dans un logiciel.

Le projet a initialement démarré dans le cadre d'un projet de la Fondation des sciences de la nature appelé "Expeditions in Computing". Ce projet a réuni un groupe de chercheurs de différentes institutions aux parcours différents, dont certains de Stanford et de l'UCSD, ainsi que des chercheurs de l'Université Tsinghua en Chine, experts dans la fabrication de dispositifs RRAM.

Efficacité énergétique : inférence de l'IA effectuée sur le gadget alimenté par batterie

Selon Weier Wan, chercheur diplômé à l'Université de Stanford et l'un des auteurs de l'article, publié hier dans Nature, NeuRRAM a été développé comme une puce d'IA qui améliore considérablement l'efficacité énergétique de l'inférence de l'IA, permettant ainsi de réaliser des fonctions d'IA complexes directement dans des appareils de périphérie alimentés par batterie, tels que des appareils portables intelligents, des drones et des capteurs IoT industriels. .

« Dans les puces d'intelligence artificielle d'aujourd'hui, le traitement et le stockage des données s'effectuent dans des endroits distincts : l'unité de calcul et l'unité de mémoire. Le mouvement fréquent de données entre ces unités consomme le plus d'énergie et devient le goulot d'étranglement pour la réalisation de processeurs d'IA à faible consommation d'énergie pour les appareils de pointe », a-t-il déclaré.

Pour résoudre ce problème, la puce NeuRRAM implémente un modèle de "calcul en mémoire", où le traitement se produit directement dans la mémoire. Il utilise également la RAM résistive (RRAM), un type de mémoire aussi rapide que la RAM statique mais non volatile, ce qui lui permet de stocker les poids du modèle AI. Une caractéristique clé des cellules RRAM est que les poids neuronaux peuvent être stockés dans les cellules mémoire sous différents niveaux de conductance, codés via des convertisseurs numérique-analogique (DAC) et transmis à la matrice mémoire.

Ce n'est pas une simulation logicielle, c'est du matériel

Il y a eu des études antérieures sur les architectures CIM, mais c'est la première à démontrer une large gamme d'applications d'IA dans le matériel plutôt que dans la simulation logicielle, tout en étant plus économe en énergie et capable d'exécuter les algorithmes avec précision, ce qu'aucune des études précédentes ont pu montrer simultanément, selon Wan.

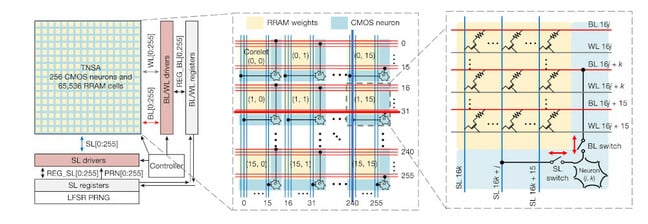

La NeuRRAM se compose de 48 cœurs CIM comprenant un total de 3 millions de cellules RRAM. Chaque noyau est décrit comme un réseau neurosynaptique transposable (TNSA) composé d'une grille de 256 × 256 cellules RRAM et de 256 circuits de neurones artificiels CMOS qui implémentent des convertisseurs analogique-numérique (ADC) et des fonctions d'activation.

Selon l'article, l'architecture TNSA a été conçue pour offrir un contrôle flexible de la direction des flux de données, ce qui est crucial pour prendre en charge une gamme variée de modèles d'IA avec différents modèles de flux de données.

Par exemple, dans les réseaux de neurones convolutionnels (CNN) qui sont courants dans les tâches liées à la vision, les données circulent dans une seule direction à travers les couches pour générer des représentations de données à différents niveaux d'abstraction, tandis que dans certains autres modèles, l'échantillonnage probabiliste est effectué dans les deux sens entre les couches. jusqu'à ce que le réseau converge vers un état à haute probabilité.

Cependant, d'autres conceptions qui ont combiné CIM avec RRAM se limitaient à fonctionner dans une seule direction, généralement en câblé des rangées et des colonnes du réseau crossbar RRAM à des circuits dédiés à la périphérie pour piloter les entrées et mesurer les sorties, indique le document.

Comment ça marche

Le secret de la reconfigurabilité de la NeuRRAM est qu'elle distribue les circuits de neurones CMOS entre les cellules RRAM et les connecte sur la longueur des lignes et des colonnes.

Chaque TNSA est décomposé en un certain nombre de corelets, dont chacun se compose de 16 × 16 cellules RRAM et d'un circuit neuronal. Les corelets sont connectés par des lignes de bit (BL) et des lignes de mot (WL) partagées le long de la direction horizontale, et des lignes de source (SL) le long de la direction verticale.

Le circuit neuronal se connecte via des commutateurs à un BL et un SL sur les 16 de chacun qui passent par le corelet, et est responsable de l'intégration des entrées de toutes les 256 RRAM se connectant au même BL ou SL.

Chaque circuit neuronal peut utiliser ses commutateurs BL et SL pour l'entrée et la sortie. Cela signifie qu'il peut recevoir la multiplication matrice-vecteur analogique (MVM) d'une cellule RRAM provenant de BL ou SL via les commutateurs, mais peut également envoyer les résultats numériques convertis aux registres périphériques via les mêmes commutateurs.

Cet agencement signifie que différentes directions de flux de données peuvent être mises en œuvre en configurant le commutateur à utiliser pendant les étapes d'entrée et de sortie de chaque circuit neuronal.

(Cette architecture nous rappelle aussi un peu Puce de processeur AI de SambaNova, qui est implémenté sous la forme d'une grille d'unités de calcul et d'unités de mémoire, reliées par une structure de communication sur puce qui contrôle le flux de données.)

Pour maximiser les performances d'inférence de l'IA à l'aide des 48 cœurs CIM de la NeuRRAM, il est possible de mettre en œuvre diverses stratégies de mappage de poids qui exploitent à la fois le parallélisme des modèles et le parallélisme des données, selon l'article.

Dans le cas d'un CNN, la stratégie pourrait consister à dupliquer les poids des premières couches les plus intensives en calcul vers plusieurs cœurs CIM pour une inférence parallèle. Le document fournit une description plus détaillée des stratégies de cartographie des poids disponibles.

L'article rapporte des résultats d'inférence mesurés par le matériel à l'aide de la puce pour une gamme de tâches d'IA, notamment des classifications d'images à l'aide d'ensembles de données CIFAR-10 et MNIST, la reconnaissance de commandes vocales Google et la récupération d'images MNIST, mises en œuvre avec divers modèles d'IA.

Il est censé atteindre une précision d'inférence comparable aux modèles logiciels entraînés avec des poids de 4 bits dans toutes ces tâches de référence. Par exemple, il atteint un taux d'erreur de 0.98 % sur la reconnaissance des chiffres manuscrits MNIST à l'aide d'un CNN à 7 couches, un taux d'erreur de 14.34 % sur la classification d'objets CIFAR-10 à l'aide de ResNet-20 et un taux d'erreur de 15.34 % sur la reconnaissance des commandes vocales de Google à l'aide d'un LSTM à 4 cellules (mémoire longue à court terme).

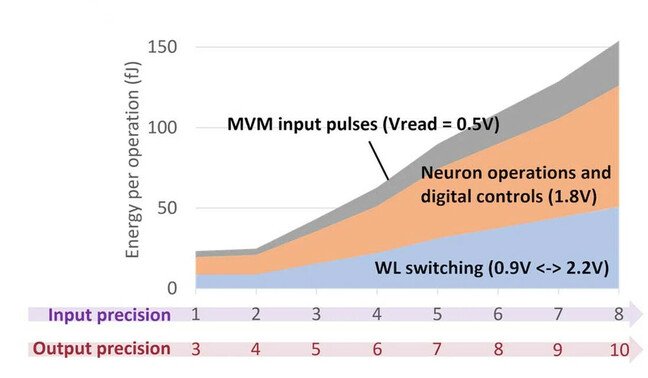

La puce NeuRRAM est également censée avoir une efficacité énergétique deux fois supérieure à celle des conceptions de puces CIM antérieures utilisant la RRAM, sur diverses précisions de calcul en bits. Cependant, la consommation d'énergie dans le document n'est pas citée sous une forme facile à comparer avec les appareils commerciaux sur le marché, et la figure ci-dessous illustre la consommation d'énergie par opération dans différentes précisions de bit mesurées en femtojoules (fJ).

Cependant, Wan nous a dit que pour une tâche typique de détection de mots clés en temps réel qui s'exécute sur de nombreux appareils domestiques intelligents aujourd'hui (comme dire à un haut-parleur intelligent d'allumer la lumière), on estime que NeuRRAM consomme moins de 2 microwatts de puissance.

"Cela signifie que même sur une petite pile bouton, elle pourrait fonctionner pendant plus de 10 ans (sans tenir compte de l'énergie consommée par les autres composants du système)", a-t-il déclaré.

Selon le document, la puce est fabriquée à l'aide d'une technologie CMOS 130 nm, et on s'attend à ce que l'efficacité énergétique s'améliore avec la mise à l'échelle de la technologie, comme c'est le cas pour d'autres produits semi-conducteurs.

Productisation encore dans des années

Alors verrons-nous un dispositif commercial d'expédition basé sur cette technologie ? Wan dit qu'il a un grand potentiel de commercialisation et envisage personnellement de travailler à le produire lui-même.

"Le cas d'utilisation initial le plus approprié est très probablement en périphérie extrême / IoT", nous a-t-il dit.

Un produit basé sur la puce NeuRRAM pourrait être combiné dans un système avec un processeur, comme avec d'autres accélérateurs, mais ce n'est pas nécessaire pour toutes les applications.

"Récemment, il y a eu une tendance à ce que les données des capteurs soient directement transmises aux processeurs d'IA sans passer par le processeur ou la mémoire supplémentaire", a déclaré Wan, mais il a ajouté que pour la plupart des cas de déploiement réels, ces accélérateurs d'IA fonctionnent comme un co-processeur pour un CPU, où le CPU gère d'autres tâches.

La puce NeuRRAM est destinée uniquement au travail d'inférence, en grande partie parce que la technologie RRAM dans sa forme actuelle n'est pas très adaptée à la formation car le processus de formation nécessite des mises à jour fréquentes de la mémoire, et c'est "une opération très coûteuse sur RRAM", a déclaré Wan.

« Actuellement, de nombreuses fonderies commerciales ont déjà la capacité de fabriquer des dispositifs RRAM, mais principalement pour des utilisations de mémoire embarquée plutôt que pour le calcul en mémoire. Une fois que le processus RRAM sera plus largement disponible pour les concepteurs de circuits intégrés, un produit NeuRRAM pourrait voir le jour.

Le calendrier exact pour que cela se produise est difficile à prévoir, cependant, et Wan a déclaré que cela pourrait être dans les deux à trois prochaines années, ou bien plus longtemps. ®

- AI

- art de l'IA

- générateur d'art ai

- robot IA

- intelligence artificielle

- certification en intelligence artificielle

- intelligence artificielle en banque

- robot d'intelligence artificielle

- robots d'intelligence artificielle

- logiciel d'intelligence artificielle

- blockchain

- conférence blockchain ai

- cognitif

- intelligence artificielle conversationnelle

- crypto conférence ai

- de dall

- l'apprentissage en profondeur

- google ai

- machine learning

- Platon

- platon ai

- Intelligence des données Platon

- Jeu de Platon

- PlatonDonnées

- jeu de platogamie

- échelle ai

- syntaxe

- Le registre

- zéphyrnet