Pour étancher la soif de modèles d'IA et d'apprentissage automatique toujours plus grands, Tesla a révélé une multitude de détails à Hot Chips 34 sur leur architecture de supercalcul entièrement personnalisée appelée Dojo.

Le système est essentiellement un supercalculateur composable massif, bien que contrairement à ce que nous voyons sur le Top 500, il est construit à partir d'une architecture entièrement personnalisée qui couvre le calcul, la mise en réseau et le silicium d'entrée/sortie (E/S) jusqu'à l'architecture de jeu d'instructions (ISA), l'alimentation, le conditionnement et le refroidissement. Tout cela a été fait dans le but exprès d'exécuter à grande échelle des algorithmes de formation d'apprentissage automatique spécifiques et personnalisés.

"Le traitement des données dans le monde réel n'est possible que grâce à des techniques d'apprentissage automatique, qu'il s'agisse du traitement du langage naturel, de la conduite dans des rues conçues pour la vision humaine ou de la robotique s'interfaçant avec l'environnement quotidien", a déclaré Ganesh Venkataramanan, directeur principal de l'ingénierie matérielle chez Tesla. lors de son discours d'ouverture.

Cependant, il a fait valoir que les méthodes traditionnelles de mise à l'échelle des charges de travail distribuées n'ont pas réussi à accélérer au rythme nécessaire pour répondre aux exigences de l'apprentissage automatique. En effet, la loi de Moore ne suffit pas et les systèmes disponibles pour la formation IA/ML à grande échelle, à savoir une combinaison de CPU/GPU ou, dans des circonstances plus rares, en utilisant des accélérateurs d'IA spécialisés, ne sont pas non plus disponibles.

«Traditionnellement, nous construisons des puces, nous les mettons sur des packages, les packages vont sur des PCB, qui vont dans des systèmes. Les systèmes vont dans des racks », a déclaré Venkataramanan. Le problème est que chaque fois que des données se déplacent de la puce vers le package et hors du package, cela entraîne une pénalité de latence et de bande passante.

Un sandwich de centre de données

Alors pour contourner les limites, Venkataramanan et son équipe ont recommencé à zéro.

"Dès mon entretien avec Elon, il m'a demandé ce que vous pouviez faire de différent des CPU et des GPU pour l'IA. J'ai l'impression que toute l'équipe répond encore à cette question.

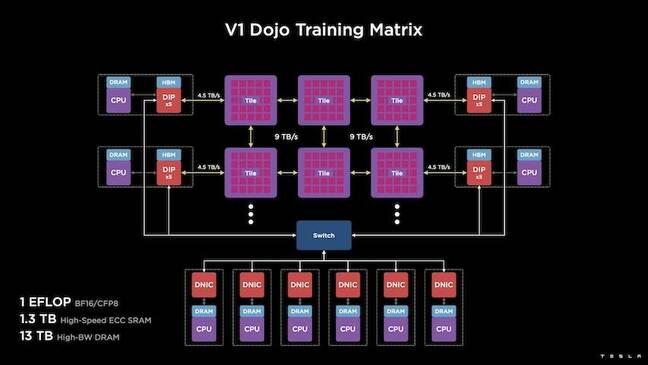

Cela a conduit au développement de la tuile de formation Dojo, un cluster de calcul autonome occupant un demi-pied cube capable de 556 TFLOPS de performances FP32 dans un boîtier refroidi par liquide de 15 kW.

Chaque dalle est équipée de 11 Go de SRAM et est connectée via une structure de 9 To/s à l'aide d'un protocole de transport personnalisé sur l'ensemble de la pile.

"Cette tuile de formation représente des quantités inégalées d'intégration de l'ordinateur à la mémoire à la fourniture d'énergie, à la communication, sans nécessiter de commutateurs supplémentaires", a déclaré Venkataramanan.

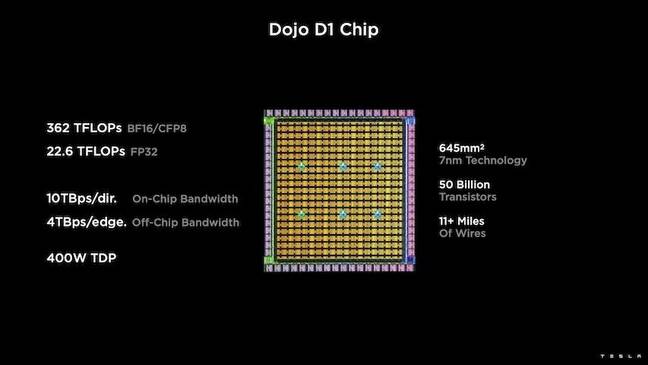

Au cœur de la tuile de formation se trouve le D1 de Tesla, une matrice de transistor de 50 milliards, basée sur le processus 7 nm de TSMC. Tesla dit que chaque D1 est capable de 22 TFLOPS de performances FP32 à un TDP de 400W. Cependant, Tesla note que la puce est capable d'exécuter une large gamme de calculs en virgule flottante, y compris quelques calculs personnalisés.

"Si vous comparez les transistors au millimètre carré, c'est probablement la pointe de la technologie de tout ce qui existe", a déclaré Venkataramanan.

Tesla a ensuite pris 25 D1, les a regroupés pour les bonnes matrices connues, puis les a emballées à l'aide de la technologie système sur plaquette de TSMC pour "réaliser une énorme quantité d'intégration de calcul avec une latence très faible et une bande passante très élevée", a-t-il déclaré.

Cependant, la conception du système sur plaquette et l'architecture empilée verticalement ont présenté des défis en matière de fourniture d'énergie.

Selon Venkataramanan, la plupart des accélérateurs placent aujourd'hui la puissance directement à côté du silicium. Et bien qu'elle ait fait ses preuves, cette approche signifie qu'une grande partie de l'accélérateur doit être dédiée à ces composants, ce qui la rendait peu pratique pour Dojo, a-t-il expliqué. Au lieu de cela, Tesla a conçu ses puces pour fournir de l'énergie directement par le bas de la matrice.

Mettre le tout ensemble

"Nous pourrions construire un centre de données entier ou un bâtiment entier à partir de cette tuile de formation, mais la tuile de formation n'est que la partie calcul. Nous devons également le nourrir », a déclaré Venkataramanan.

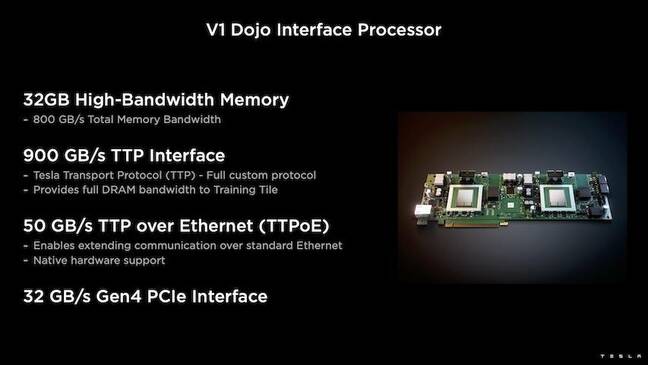

Pour cela, Tesla a également développé le processeur d'interface Dojo (DIP), qui fonctionne comme un pont entre le processeur hôte et les processeurs de formation. Le DIP sert également de source de mémoire partagée à large bande passante (HBM) et de carte réseau à haut débit de 400 Gbit/s.

Chaque DIP dispose de 32 Go de HBM et jusqu'à cinq de ces cartes peuvent être connectées à une tuile de formation à 900 Go/s pour un total de 4.5 To/s vers l'hôte pour un total de 160 Go de HBM par tuile.

Les paires de configuration V1 de Tesla de ces tuiles - ou 150 matrices D1 - en matrice prenaient en charge quatre processeurs hôtes équipés chacun de cinq cartes DIP pour obtenir un exaflop revendiqué de performances BF16 ou CFP8.

Mis ensemble, Venkataramanan dit l'architecture - détaillée en profondeur ici by La prochaine plateforme – permet à Tesla de surmonter les limitations associées aux accélérateurs traditionnels tels que Nvidia et AMD.

"Comment fonctionnent les accélérateurs traditionnels, vous essayez généralement d'adapter un modèle entier à chaque accélérateur. Répliquez-le, puis faites passer les données à travers chacun d'eux », a-t-il déclaré. « Que se passe-t-il si nous avons des modèles de plus en plus gros ? Ces accélérateurs peuvent tomber à plat parce qu'ils manquent de mémoire.

Ce n'est pas un problème nouveau, a-t-il noté. Le commutateur NV de Nvidia, par exemple, permet de mutualiser la mémoire sur de grandes banques de GPU. Cependant, Venkataramanan soutient que cela ajoute non seulement de la complexité, mais introduit une latence et des compromis sur la bande passante.

« Nous y avons pensé dès le départ. Nos tuiles de calcul et chacune des matrices ont été conçues pour s'adapter à de grands modèles », a déclaré Venkataramanan.

Logiciels

Une telle architecture de calcul spécialisée nécessite une pile logicielle spécialisée. Cependant, Venkataramanan et son équipe ont reconnu que la programmabilité ferait ou détruirait Dojo.

"La facilité de programmabilité pour les homologues logiciels est primordiale lorsque nous concevons ces systèmes", a-t-il déclaré. "Les chercheurs n'attendront pas que vos logiciels écrivent un noyau manuscrit pour s'adapter à un nouvel algorithme que nous voulons exécuter."

Pour ce faire, Tesla a abandonné l'idée d'utiliser des noyaux et a conçu l'architecture de Dojo autour de compilateurs.

"Ce que nous avons fait, c'est que nous avons utilisé PiTorch. Nous avons créé une couche intermédiaire, qui nous aide à paralléliser pour faire évoluer le matériel en dessous. Sous tout, il y a du code compilé », a-t-il déclaré. "C'est le seul moyen de créer des piles logicielles adaptables à toutes ces futures charges de travail."

Malgré l'accent mis sur la flexibilité du logiciel, Venkataramanan note que la plate-forme, qui fonctionne actuellement dans leurs laboratoires, est limitée à l'utilisation de Tesla pour le moment.

"Nous nous concentrons d'abord sur nos clients internes", a-t-il déclaré. « Elon a rendu public qu'au fil du temps, nous mettrons cela à la disposition des chercheurs, mais nous n'avons pas de délai pour cela. ®

- AI

- art de l'IA

- générateur d'art ai

- robot IA

- intelligence artificielle

- certification en intelligence artificielle

- intelligence artificielle en banque

- robot d'intelligence artificielle

- robots d'intelligence artificielle

- logiciel d'intelligence artificielle

- blockchain

- conférence blockchain ai

- cognitif

- intelligence artificielle conversationnelle

- crypto conférence ai

- de dall

- l'apprentissage en profondeur

- google ai

- machine learning

- Platon

- platon ai

- Intelligence des données Platon

- Jeu de Platon

- PlatonDonnées

- jeu de platogamie

- échelle ai

- syntaxe

- Le registre

- zéphyrnet