एक नया प्रकाशित शोध पत्र एक कंप्यूट-इन-मेमोरी (सीआईएम) चिप का वर्णन करता है जो कृत्रिम न्यूरॉन्स को प्रतिरोधी रैम (आरआरएएम) के साथ जोड़ती है ताकि एआई मॉडल वजन उसी चिप पर संग्रहीत और संसाधित किया जा सके।

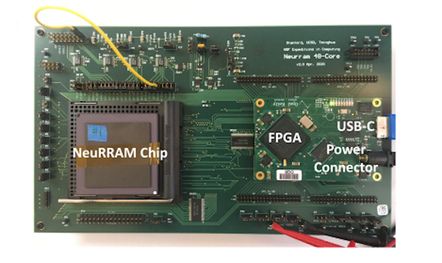

प्रतिरोधक रैंडम-एक्सेस मेमोरी पर आधारित एक कंप्यूट-इन-मेमोरी चिप (बड़ा करने के लिए क्लिक करें)। छवि: वान एट अल

डिजाइन के पीछे शोधकर्ताओं का दावा है कि यह किनारे के अनुप्रयोगों के लिए अधिक कुशल होगा क्योंकि यह अलग-अलग गणना और मेमोरी ब्लॉक के बीच डेटा आंदोलन को समाप्त करता है।

एज कंप्यूटिंग और आर्टिफिशियल इंटेलिजेंस दोनों निकट भविष्य में उल्कापिंड विकास के लिए ट्रैक पर हैं, कम से कम विश्लेषक कंपनी IDC . के अनुसार. कुछ परिदृश्य उन्हें एक साथ जोड़ते हैं क्योंकि किनारे की तैनाती शक्ति और कनेक्टिविटी पर विवश हो सकती है, फिर भी डेटा की महत्वपूर्ण मात्रा का विश्लेषण करने और घटनाओं के लिए वास्तविक समय की प्रतिक्रिया देने की आवश्यकता होती है, जिससे डिवाइस में एआई मॉडल "लिविंग" सबसे इष्टतम समाधान बन जाता है। .

इसके प्रकाश में, शोधकर्ताओं के एक समूह ने एक चिप विकसित की है जिसे इसे न्यूरोराम कहते हैं, क्योंकि यह एक उपन्यास वास्तुकला में आरआरएएम के साथ कृत्रिम न्यूरॉन्स को जोड़ती है। परियोजना का लक्ष्य एक ऐसा डिज़ाइन प्रदान करना था जो एक साथ उच्च ऊर्जा दक्षता के साथ-साथ विभिन्न एआई मॉडल का समर्थन करने के लिए बहुमुखी प्रतिभा और सॉफ्टवेयर में एक ही मॉडल को चलाने के लिए तुलनीय सटीकता प्रदान कर सके।

परियोजना शुरू में एक नेचर साइंस फाउंडेशन परियोजना के हिस्से के रूप में शुरू हुई जिसे "कंप्यूटिंग में अभियान" कहा जाता है। इस परियोजना ने अलग-अलग पृष्ठभूमि वाले विभिन्न संस्थानों के शोधकर्ताओं के एक समूह को इकट्ठा किया, जिनमें कुछ स्टैनफोर्ड और यूसीएसडी के साथ-साथ चीन में सिंघुआ विश्वविद्यालय के शोधकर्ता शामिल हैं जो आरआरएएम डिवाइस निर्माण में विशेषज्ञ हैं।

ऊर्जा दक्षता: बैटरी से चलने वाले उपकरण पर किया गया AI अनुमान

वीयर वान के अनुसार, स्टैनफोर्ड विश्वविद्यालय में स्नातक शोधकर्ता और उनमें से एक कागज के लेखक, नेचर में कल प्रकाशित किया गया था, न्यूरराम को एआई चिप के रूप में विकसित किया गया है जो एआई अनुमान की ऊर्जा दक्षता में काफी सुधार करता है, जिससे जटिल एआई कार्यों को सीधे बैटरी से चलने वाले एज डिवाइस, जैसे स्मार्ट वियरेबल, ड्रोन और औद्योगिक IoT सेंसर के भीतर महसूस किया जा सकता है। .

"आज के एआई चिप्स में, डेटा प्रोसेसिंग और डेटा स्टोरेज अलग-अलग जगहों पर होता है - कंप्यूटिंग यूनिट और मेमोरी यूनिट। इन इकाइयों के बीच लगातार डेटा की आवाजाही सबसे अधिक ऊर्जा की खपत करती है और एज डिवाइसों के लिए कम-शक्ति वाले एआई प्रोसेसर को साकार करने में अड़चन बन जाती है, ”उन्होंने कहा।

इसे संबोधित करने के लिए, न्यूरराम चिप "कम्प्यूट-इन-मेमोरी" मॉडल लागू करता है, जहां प्रसंस्करण सीधे स्मृति के भीतर होता है। यह प्रतिरोधी रैम (आरआरएएम) का भी उपयोग करता है, एक मेमोरी प्रकार जो स्थिर रैम जितना तेज़ होता है लेकिन गैर-वाष्पशील होता है, जिससे यह एआई मॉडल वजन को स्टोर करने की इजाजत देता है। आरआरएएम कोशिकाओं की एक प्रमुख विशेषता यह है कि तंत्रिका भार को स्मृति कोशिकाओं में विभिन्न चालन स्तरों के रूप में संग्रहीत किया जा सकता है, डिजिटल-से-एनालॉग कन्वर्टर्स (डीएसी) के माध्यम से एन्कोड किया जाता है और मेमोरी सरणी को खिलाया जाता है।

यह एक सॉफ्टवेयर सिमुलेशन नहीं है, यह हार्डवेयर है

सीआईएम आर्किटेक्चर पर पिछले अध्ययन हुए हैं, लेकिन सॉफ्टवेयर सिमुलेशन के बजाय हार्डवेयर में एआई अनुप्रयोगों की एक विस्तृत श्रृंखला प्रदर्शित करने वाला यह पहला है, जबकि अधिक ऊर्जा कुशल और एल्गोरिदम को सटीक रूप से चलाने में सक्षम होने के कारण, पिछले अध्ययनों में से कुछ भी नहीं वान के अनुसार, एक साथ दिखाने में सक्षम थे।

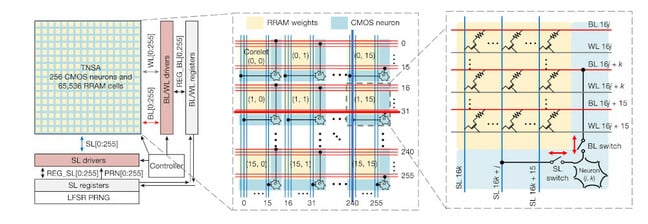

NeuRRAM में 48 CIM कोर होते हैं, जिसमें कुल 3 मिलियन RRAM सेल होते हैं। प्रत्येक कोर को एक ट्रांसपोज़ेबल न्यूरोसिनेप्टिक सरणी (TNSA) के रूप में वर्णित किया गया है जिसमें 256 × 256 RRAM कोशिकाओं और 256 CMOS कृत्रिम न्यूरॉन सर्किट का ग्रिड होता है जो एनालॉग-टू-डिजिटल कन्वर्टर्स (ADCs) और सक्रियण कार्यों को लागू करता है।

कागज के अनुसार, TNSA आर्किटेक्चर को डेटा प्रवाह की दिशा के लचीले नियंत्रण की पेशकश करने के लिए डिज़ाइन किया गया है, जो विभिन्न डेटाफ़्लो पैटर्न के साथ AI मॉडल की एक विविध श्रेणी का समर्थन करने के लिए महत्वपूर्ण है।

उदाहरण के लिए, दृढ़ तंत्रिका नेटवर्क (सीएनएन) में जो दृष्टि से संबंधित कार्यों में आम हैं, डेटा अलग-अलग अमूर्त स्तरों पर डेटा प्रतिनिधित्व उत्पन्न करने के लिए परतों के माध्यम से एक ही दिशा में प्रवाहित होता है, जबकि कुछ अन्य मॉडलों में संभाव्य नमूनाकरण परतों के बीच आगे और पीछे किया जाता है। जब तक नेटवर्क एक उच्च-संभाव्यता स्थिति में परिवर्तित नहीं हो जाता।

हालांकि, अन्य डिजाइन जिन्होंने सीआईएम को आरआरएएम के साथ जोड़ा है, वे एक ही दिशा में संचालन तक सीमित थे, आमतौर पर आरआरएएम क्रॉसबार सरणी की पंक्तियों और स्तंभों को हार्डवायरिंग द्वारा परिधि पर समर्पित सर्किट के लिए इनपुट ड्राइव और आउटपुट को मापने के लिए, पेपर कहता है।

यह कैसे काम करता है

न्यूरराम की पुन: विन्यास का रहस्य यह है कि यह सीएमओएस न्यूरॉन सर्किट को आरआरएएम कोशिकाओं के बीच वितरित करता है, और उन्हें पंक्तियों और स्तंभों दोनों की लंबाई के साथ जोड़ता है।

प्रत्येक TNSA को कई कोरलेट्स में विभाजित किया जाता है, जिनमें से प्रत्येक में 16 × 16 RRAM सेल और एक न्यूरॉन सर्किट होता है। कोरलेट क्षैतिज दिशा के साथ साझा बिट-लाइन (बीएल) और वर्ड-लाइन (डब्ल्यूएल) और ऊर्ध्वाधर दिशा के साथ स्रोत-लाइन (एसएल) से जुड़े होते हैं।

न्यूरॉन सर्किट स्विच के माध्यम से एक बीएल और प्रत्येक के 16 में से एक एसएल से जुड़ता है जो कोरलेट से गुजरता है, और एक ही बीएल या एसएल से जुड़ने वाले सभी 256 आरआरएएम से इनपुट को एकीकृत करने के लिए जिम्मेदार है।

प्रत्येक न्यूरॉन सर्किट इनपुट और आउटपुट के लिए अपने बीएल और एसएल स्विच का उपयोग कर सकता है। इसका मतलब है कि यह स्विच के माध्यम से बीएल या एसएल से आने वाले आरआरएएम सेल से एनालॉग मैट्रिक्स-वेक्टर गुणन (एमवीएम) प्राप्त कर सकता है, लेकिन उसी स्विच के माध्यम से परिवर्तित डिजिटल परिणाम परिधीय रजिस्टरों को भी भेज सकता है।

इस व्यवस्था का मतलब है कि प्रत्येक न्यूरॉन सर्किट के इनपुट और आउटपुट चरणों के दौरान किस स्विच का उपयोग करना है, इसे कॉन्फ़िगर करके अलग-अलग डेटाफ्लो दिशाओं को लागू किया जा सकता है।

(यह वास्तुकला हमें कुछ हद तक ध्यान में रखती है सांबानोवा की एआई प्रोसेसर चिप, जिसे कंप्यूट इकाइयों और मेमोरी इकाइयों के ग्रिड के रूप में कार्यान्वित किया जाता है, जो डेटा प्रवाह को नियंत्रित करने वाले ऑन-चिप संचार कपड़े से जुड़ा होता है।)

पेपर के अनुसार, न्यूरराम में 48 सीआईएम कोर का उपयोग करके एआई अनुमान प्रदर्शन को अधिकतम करने के लिए, विभिन्न वजन-मानचित्रण रणनीतियों को लागू करना संभव है जो मॉडल समानता और डेटा समांतरता दोनों का फायदा उठाते हैं।

सीएनएन के मामले में, रणनीति समानांतर अनुमान के लिए कई सीआईएम कोर के लिए प्रारंभिक, सबसे कम्प्यूटेशनल रूप से गहन परतों के वजन को डुप्लिकेट करने की हो सकती है। पेपर उपलब्ध वजन-मानचित्रण रणनीतियों का अधिक विस्तृत विवरण प्रदान करता है।

पेपर एआई कार्यों की एक श्रृंखला के लिए चिप का उपयोग करके हार्डवेयर-मापा निष्कर्ष परिणामों की रिपोर्ट करता है जिसमें सीआईएफएआर -10 और एमएनआईएसटी डेटासेट का उपयोग करके छवि वर्गीकरण, Google भाषण कमांड मान्यता और एमएनआईएसटी छवि पुनर्प्राप्ति, विभिन्न एआई मॉडल के साथ कार्यान्वित किया जाता है।

इन सभी बेंचमार्क कार्यों में 4-बिट भार के साथ प्रशिक्षित सॉफ़्टवेयर मॉडल की तुलना में अनुमान सटीकता प्राप्त करने का दावा किया जाता है। उदाहरण के लिए, यह 0.98-लेयर CNN का उपयोग करके MNIST हस्तलिखित अंकों की पहचान पर 7 प्रतिशत त्रुटि दर, ResNet-14.34 का उपयोग करके CIFAR-10 ऑब्जेक्ट वर्गीकरण पर 20 प्रतिशत त्रुटि दर और Google स्पीच कमांड रिकग्निशन पर 15.34 प्रतिशत त्रुटि दर प्राप्त करता है। 4-सेल LSTM (दीर्घकालिक अल्पकालिक स्मृति)।

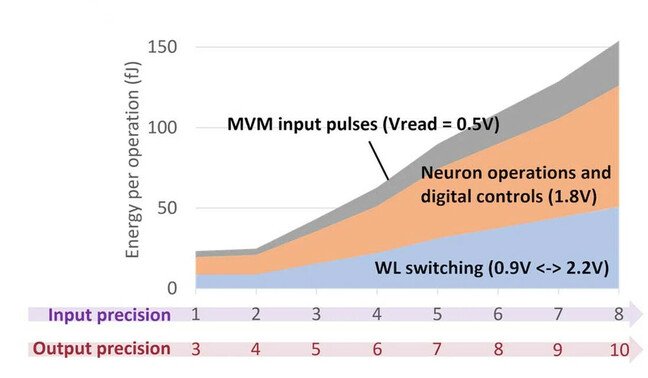

यह भी दावा किया जाता है कि न्यूरराम चिप में ऊर्जा दक्षता है जो विभिन्न कम्प्यूटेशनल बिट परिशुद्धताओं में आरआरएएम का उपयोग करके पहले सीआईएम चिप डिजाइनों की तुलना में दो गुना बेहतर है। हालांकि, कागज में ऊर्जा खपत को ऐसे रूप में उद्धृत नहीं किया गया है जो बाजार पर वाणिज्यिक उपकरणों के साथ तुलना करना आसान है, और नीचे दिखाया गया आंकड़ा femtojoules (fJ) में मापा गया विभिन्न बिट परिशुद्धता में प्रति ऑपरेशन ऊर्जा खपत को दिखाता है।

हालांकि, वान ने हमें बताया कि एक सामान्य रीयल-टाइम कीवर्ड स्पॉटिंग कार्य के लिए जो आज कई स्मार्ट घरेलू उपकरणों पर चलता है (जैसे कि स्मार्ट स्पीकर को प्रकाश चालू करने के लिए कहना), न्यूरराम का अनुमान है कि 2 माइक्रोवाट से कम बिजली की खपत होगी।

"इसका मतलब है कि एक छोटी सिक्का बैटरी पर भी, यह 10 से अधिक वर्षों तक चल सकता है (अन्य सिस्टम घटकों द्वारा खपत बिजली पर विचार नहीं करते)," उन्होंने कहा।

कागज के अनुसार, चिप को 130nm CMOS तकनीक का उपयोग करके बनाया गया है, और यह उम्मीद की जाती है कि प्रौद्योगिकी स्केलिंग के साथ ऊर्जा दक्षता में सुधार होगा, जैसा कि अन्य अर्धचालक उत्पादों के मामले में है।

उत्पादन में अभी साल बाकी हैं

तो क्या हम इस तकनीक पर आधारित शिपिंग वाणिज्यिक उपकरण देखेंगे? वान का कहना है कि इसके व्यावसायीकरण की काफी संभावनाएं हैं, और व्यक्तिगत रूप से इसे स्वयं उत्पादित करने पर काम करने पर विचार कर रहे हैं।

"सबसे उपयुक्त प्रारंभिक उपयोग का मामला चरम किनारे / IoT में होने की संभावना है," उन्होंने हमें बताया।

न्यूरराम चिप पर आधारित उत्पाद को एक सिस्टम में सीपीयू के साथ जोड़ा जा सकता है, जैसा कि अन्य त्वरक के साथ होता है, लेकिन यह हर एप्लिकेशन के लिए आवश्यक नहीं है।

वान ने कहा, "हाल ही में सीपीयू या अतिरिक्त मेमोरी से गुजरे बिना सेंसर से डेटा सीधे एआई प्रोसेसर को फीड करने का चलन रहा है, लेकिन उन्होंने कहा कि अधिकांश वास्तविक दुनिया की तैनाती के मामलों में, ऐसे एआई त्वरक एक सह-प्रोसेसर के रूप में कार्य करते हैं। सीपीयू के लिए, जहां सीपीयू अन्य कार्यों का प्रबंधन करता है।

वान ने कहा कि न्यूरराम चिप केवल अनुमान लगाने के काम के लिए है, मुख्यतः क्योंकि आरआरएएम तकनीक अपने वर्तमान स्वरूप में प्रशिक्षण के लिए बहुत उपयुक्त नहीं है क्योंकि प्रशिक्षण प्रक्रिया को मेमोरी में लगातार अपडेट की आवश्यकता होती है, और यह "आरआरएएम पर एक बहुत महंगा ऑपरेशन" है।

"वर्तमान में कई वाणिज्यिक फाउंड्री में पहले से ही आरआरएएम उपकरणों को बनाने की क्षमता है, लेकिन ज्यादातर कंप्यूट-इन-मेमोरी के बजाय एम्बेडेड मेमोरी उपयोग के लिए। एक बार जब RRAM प्रक्रिया IC डिजाइनरों के लिए अधिक व्यापक रूप से उपलब्ध हो जाती है, तो एक NeuRRAM उत्पाद हो सकता है।"

ऐसा होने के लिए सटीक समयरेखा भविष्यवाणी करना मुश्किल है, और वान ने कहा कि अगले दो से तीन वर्षों में, या उससे अधिक हो सकता है। ®

- AI

- ai कला

- ऐ कला जनरेटर

- ऐ रोबोट

- कृत्रिम बुद्धिमत्ता

- कृत्रिम बुद्धिमत्ता प्रमाणन

- बैंकिंग में आर्टिफिशियल इंटेलिजेंस

- आर्टिफिशियल इंटेलिजेंस रोबोट

- आर्टिफिशियल इंटेलिजेंस रोबोट

- कृत्रिम बुद्धि सॉफ्टवेयर

- blockchain

- ब्लॉकचेन सम्मेलन एआई

- कॉइनजीनियस

- संवादी कृत्रिम बुद्धिमत्ता

- क्रिप्टो सम्मेलन एआई

- दल-ए

- ध्यान लगा के पढ़ना या सीखना

- इसे गूगल करें

- यंत्र अधिगम

- प्लेटो

- प्लेटो एआई

- प्लेटो डेटा इंटेलिजेंस

- प्लेटो गेम

- प्लेटोडाटा

- प्लेटोगेमिंग

- स्केल एआई

- वाक्यविन्यास

- रजिस्टर

- जेफिरनेट