Un documento di ricerca appena pubblicato descrive un chip compute-in-memory (CIM) che combina neuroni artificiali con RAM resistiva (RRAM) in modo che i pesi del modello AI possano essere archiviati ed elaborati sullo stesso chip.

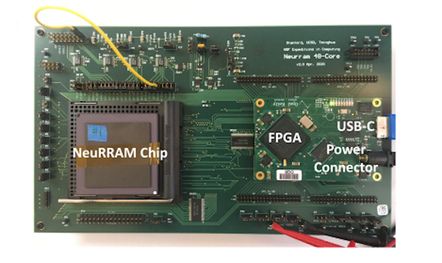

Un chip compute-in-memory basato sulla memoria resistiva ad accesso casuale (fare clic per ingrandire). Immagine: Wan et al

I ricercatori dietro il progetto affermano che sarebbe più efficiente per le applicazioni edge perché elimina lo spostamento dei dati tra blocchi di calcolo e memoria separati.

L’edge computing e l’intelligenza artificiale sono entrambi sulla buona strada per una crescita fulminea, almeno nel prossimo futuro secondo la società di analisi IDC. Alcuni scenari li combinano insieme perché le implementazioni edge possono essere limitate in termini di potenza e connettività, ma devono comunque analizzare volumi significativi di dati e fornire una risposta quasi in tempo reale agli eventi, rendendo un modello di intelligenza artificiale “vivente” nel dispositivo la soluzione più ottimale .

Alla luce di ciò, un gruppo di ricercatori ha sviluppato un chip chiamato NeuRRAM, perché combina neuroni artificiali con RRAM in una nuova architettura. L’obiettivo del progetto era quello di fornire un design in grado di fornire contemporaneamente un’elevata efficienza energetica, nonché la versatilità per supportare vari modelli di intelligenza artificiale e una precisione paragonabile all’esecuzione dello stesso modello nel software.

Il progetto inizialmente è iniziato come parte di un progetto della Nature Science Foundation chiamato “Expeditions in Computing”. Questo progetto ha riunito un gruppo di ricercatori provenienti da diverse istituzioni con background diversi, tra cui alcuni di Stanford e UCSD, nonché ricercatori dell’Università di Tsinghua in Cina, esperti nella fabbricazione di dispositivi RRAM.

Efficienza energetica: inferenza dell'intelligenza artificiale eseguita sul gizmo alimentato a batteria

Secondo Weier Wan, ricercatore laureato presso l'Università di Stanford e uno dei autori dell'articolo, pubblicato ieri su Nature, NeuRRAM è stato sviluppato come un chip AI che migliora notevolmente l'efficienza energetica dell'inferenza AI, consentendo così di realizzare funzioni AI complesse direttamente all'interno di dispositivi edge alimentati a batteria, come dispositivi indossabili intelligenti, droni e sensori IoT industriali. .

“Nei chip AI di oggi, l'elaborazione e l'archiviazione dei dati avvengono in luoghi separati: unità di calcolo e unità di memoria. Il frequente spostamento dei dati tra queste unità consuma più energia e diventa il collo di bottiglia per la realizzazione di processori IA a basso consumo per dispositivi edge”, ha affermato.

Per risolvere questo problema, il chip NeuRRAM implementa un modello “compute-in-memory”, in cui l’elaborazione avviene direttamente all’interno della memoria. Utilizza anche la RAM resistiva (RRAM), un tipo di memoria veloce quanto la RAM statica ma non volatile, che consente di memorizzare i pesi dei modelli AI. Una caratteristica chiave delle celle RRAM è che i pesi neurali possono essere archiviati nelle celle di memoria come diversi livelli di conduttanza, codificati tramite convertitori digitale-analogico (DAC) e alimentati nell'array di memoria.

Questa non è una simulazione software, è hardware

Sono stati condotti studi precedenti sulle architetture CIM, ma questo è il primo a dimostrare un'ampia gamma di applicazioni di intelligenza artificiale nell'hardware piuttosto che nella simulazione software, pur essendo più efficienti dal punto di vista energetico e in grado di eseguire gli algoritmi in modo accurato, qualcosa che nessuno degli studi precedenti erano in grado di mostrare simultaneamente, secondo Wan.

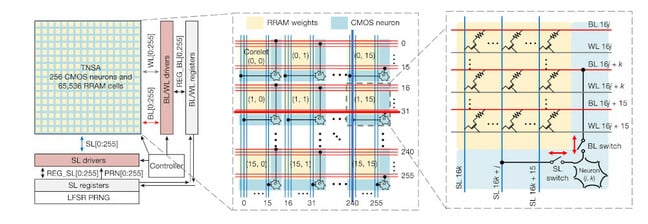

La NeuRRAM è composta da 48 core CIM per un totale di 3 milioni di celle RRAM. Ciascun nucleo è descritto come un array neurosinaptico trasponibile (TNSA) costituito da una griglia di 256 × 256 celle RRAM e 256 circuiti neuronali artificiali CMOS che implementano convertitori analogico-digitali (ADC) e funzioni di attivazione.

Secondo lo studio, l’architettura TNSA è stata progettata per offrire un controllo flessibile della direzione dei flussi di dati, che è fondamentale per supportare una vasta gamma di modelli di intelligenza artificiale con diversi modelli di flusso di dati.

Ad esempio, nelle reti neurali convoluzionali (CNN) comuni nelle attività legate alla vista, i dati fluiscono in un'unica direzione attraverso i livelli per generare rappresentazioni dei dati a diversi livelli di astrazione, mentre in alcuni altri modelli il campionamento probabilistico viene eseguito avanti e indietro tra i livelli finché la rete non converge in uno stato ad alta probabilità.

Tuttavia, altri progetti che hanno combinato CIM con RRAM si limitavano a funzionare in un'unica direzione, in genere cablando righe e colonne del crossbar array RRAM a circuiti dedicati sulla periferia per pilotare input e misurare output, afferma il documento.

Come funziona

Il segreto della riconfigurabilità della NeuRRAM è che distribuisce i circuiti dei neuroni CMOS tra le celle RRAM e li collega lungo sia le righe che le colonne.

Ogni TNSA è suddiviso in un numero di coreletti, ciascuno dei quali è costituito da 16 × 16 cellule RRAM e un circuito neuronale. I corelet sono collegati da bit-line (BL) e word-line (WL) condivise lungo la direzione orizzontale e source-line (SL) lungo la direzione verticale.

Il circuito neuronale si collega tramite interruttori a un BL e a un SL dei 16 ciascuno che passano attraverso il corelet ed è responsabile dell'integrazione degli input da tutti i 256 RRAM che si collegano allo stesso BL o SL.

Ogni circuito neuronale può utilizzare i suoi interruttori BL e SL per input e output. Ciò significa che può ricevere la moltiplicazione matrice-vettore analogica (MVM) da una cella RRAM proveniente da BL o SL attraverso gli interruttori, ma può anche inviare i risultati digitali convertiti ai registri periferici attraverso gli stessi interruttori.

Questa disposizione significa che è possibile implementare diverse direzioni del flusso di dati configurando quale interruttore utilizzare durante le fasi di input e output di ciascun circuito neuronale.

(Questa architettura ci fa venire in mente anche un po’ di Chip del processore AI di SambaNova, che è implementato come una griglia di unità di calcolo e unità di memoria, collegate da un tessuto di comunicazione su chip che controlla il flusso di dati.)

Secondo il documento, per massimizzare le prestazioni di inferenza dell'intelligenza artificiale utilizzando i 48 core CIM nella NeuRRAM, è possibile implementare varie strategie di mappatura del peso che sfruttano sia il parallelismo dei modelli che il parallelismo dei dati.

Nel caso di una CNN, la strategia potrebbe essere quella di duplicare i pesi dei primi strati, quelli più intensivi dal punto di vista computazionale, su più core CIM per l'inferenza parallela. Il documento fornisce una descrizione più dettagliata delle strategie di mappatura del peso disponibili.

Il documento riporta i risultati dell’inferenza misurati dall’hardware utilizzando il chip per una serie di attività di intelligenza artificiale, tra cui classificazioni di immagini utilizzando set di dati CIFAR-10 e MNIST, riconoscimento dei comandi vocali di Google e recupero di immagini MNIST, implementati con vari modelli di intelligenza artificiale.

Si afferma che raggiunga una precisione di inferenza paragonabile a modelli software addestrati con pesi a 4 bit in tutte queste attività di benchmark. Ad esempio, raggiunge un tasso di errore dello 0.98% sul riconoscimento delle cifre scritte a mano MNIST utilizzando una CNN a 7 livelli, un tasso di errore del 14.34% sulla classificazione degli oggetti CIFAR-10 utilizzando ResNet-20 e un tasso di errore del 15.34% sul riconoscimento dei comandi vocali di Google utilizzando un LSTM a 4 celle (memoria a lungo termine).

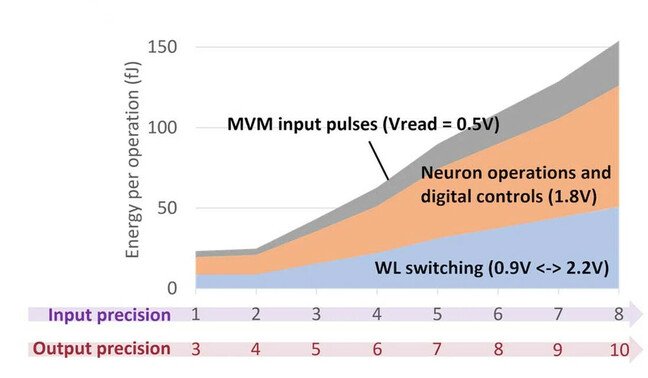

Si afferma inoltre che il chip NeuRRAM abbia un'efficienza energetica due volte migliore rispetto ai precedenti progetti di chip CIM che utilizzavano RRAM, con varie precisezze di bit computazionali. Tuttavia, il consumo di energia nel documento non è indicato in una forma facilmente confrontabile con i dispositivi commerciali sul mercato e la figura mostrata di seguito illustra il consumo di energia per operazione con diverse precisezze di bit misurato in femtojoule (fJ).

Tuttavia, Wan ci ha detto che per una tipica attività di individuazione di parole chiave in tempo reale eseguita oggi su molti dispositivi domestici intelligenti (come dire a un altoparlante intelligente di accendere la luce), si stima che NeuRRAM consumi meno di 2 microwatt di energia.

"Ciò significa che anche una piccola batteria a bottone potrebbe funzionare per più di 10 anni (senza considerare l'energia consumata da altri componenti del sistema)", ha affermato.

Secondo il documento, il chip è fabbricato utilizzando una tecnologia CMOS da 130 nm e si prevede che l'efficienza energetica migliorerà con il ridimensionamento della tecnologia, come nel caso di altri prodotti a semiconduttori.

La produzione è ancora lontana anni

Vedremo quindi un dispositivo commerciale per la spedizione basato su questa tecnologia? Wan dice che ha un grande potenziale per essere commercializzato e sta valutando personalmente la possibilità di produrlo lui stesso.

"Il caso d'uso iniziale più adatto è molto probabilmente nell'edge estremo/IoT", ci ha detto.

Un prodotto basato sul chip NeuRRAM potrebbe essere combinato in un sistema con CPU, come con altri acceleratori, ma ciò non è necessario per ogni applicazione.

"Recentemente si è verificata una tendenza in cui i dati provenienti dai sensori vengono inviati direttamente ai processori di intelligenza artificiale senza passare attraverso CPU o memoria aggiuntiva", ha affermato Wan, ma ha aggiunto che per la maggior parte dei casi di implementazione nel mondo reale, tali acceleratori di intelligenza artificiale funzionano come un coprocessore. per una CPU, dove la CPU gestisce altre attività.

Il chip NeuRRAM è destinato solo al lavoro di inferenza, soprattutto perché la tecnologia RRAM nella sua forma attuale non è molto adatta per l'addestramento perché il processo di addestramento richiede frequenti aggiornamenti della memoria, e questa è "un'operazione molto costosa su RRAM", ha detto Wan.

“Attualmente molte fonderie commerciali hanno già la capacità di fabbricare dispositivi RRAM, ma principalmente per usi di memoria incorporata piuttosto che per il calcolo in memoria. Una volta che il processo RRAM diventerà più ampiamente disponibile per i progettisti di circuiti integrati, potrebbe nascere un prodotto NeuRRAM”.

Tuttavia, la tempistica esatta in cui ciò accadrà è difficile da prevedere e Wan ha affermato che potrebbe essere nei prossimi due o tre anni, o molto più a lungo. ®

- AI

- oh arte

- generatore d'arte

- un robot

- intelligenza artificiale

- certificazione di intelligenza artificiale

- intelligenza artificiale nel settore bancario

- robot di intelligenza artificiale

- robot di intelligenza artificiale

- software di intelligenza artificiale

- blockchain

- conferenza blockchain ai

- geniale

- intelligenza artificiale conversazionale

- criptoconferenza ai

- dall's

- apprendimento profondo

- google ai

- machine learning

- Platone

- platone ai

- Platone Data Intelligence

- Gioco di Platone

- PlatoneDati

- gioco di plato

- scala ai

- sintassi

- Il registro

- zefiro