新たに発表された研究論文では、AI モデルの重みを同じチップに保存して処理できるように、人工ニューロンと抵抗性 RAM (RRAM) を組み合わせたコンピューティング イン メモリ (CIM) チップについて説明しています。

この設計の背後にいる研究者は、個別の計算ブロックとメモリ ブロック間のデータ移動がなくなるため、エッジ アプリケーションにとってより効率的であると主張しています。

エッジ コンピューティングと人工知能はどちらも、少なくとも近い将来、急速に成長する予定です。 アナリスト企業IDCによると. 一部のシナリオでは、エッジ展開が電力と接続性に制約される可能性があるため、それらを組み合わせますが、依然として大量のデータを分析し、イベントにほぼリアルタイムで応答する必要があり、デバイス内に「存在する」AI モデルが最適なソリューションになります。 .

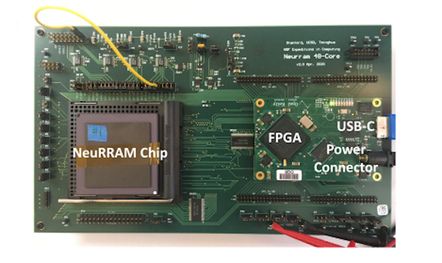

これに照らして、研究者グループはNeuRRAMと呼ばれるチップを開発しました。これは、人工ニューロンとRRAMを新しいアーキテクチャで組み合わせたものです。 このプロジェクトの目標は、高いエネルギー効率と、さまざまな AI モデルをサポートする汎用性、およびソフトウェアで同じモデルを実行する場合と同等の精度を同時に提供できる設計を提供することでした。

このプロジェクトは当初、「Expeditions in Computing」と呼ばれる Nature Science Foundation プロジェクトの一環として開始されました。 このプロジェクトには、スタンフォード大学や UCSD の研究者、RRAM デバイス製造の専門家である中国の清華大学の研究者など、さまざまなバックグラウンドを持つさまざまな機関の研究者グループが集まりました。

エネルギー効率: バッテリー駆動のギズモで行われる AI 推論

スタンフォード大学の大学院研究員であり、 論文の著者昨日Natureに掲載されたNeuRRAMは、AI推論のエネルギー効率を大幅に改善するAIチップとして開発され、スマートウェアラブル、ドローン、産業用IoTセンサーなどのバッテリー駆動のエッジデバイス内で複雑なAI機能を直接実現できるようになりました。 .

「今日の AI チップでは、データ処理とデータ ストレージは別々の場所 (コンピューティング ユニットとメモリ ユニット) で行われます。 これらのユニット間の頻繁なデータ移動は、最も多くのエネルギーを消費し、エッジ デバイス用の低電力 AI プロセッサを実現するためのボトルネックになります。」

これに対処するために、NeuRRAM チップは、処理がメモリ内で直接行われる「compute-in-memory」モデルを実装しています。 また、スタティック RAM と同じくらい高速でありながら不揮発性のメモリ タイプである抵抗性 RAM (RRAM) を利用して、AI モデルの重みを保存できます。 RRAM セルの重要な特徴は、神経の重みをさまざまなコンダクタンス レベルとしてメモリ セルに格納し、デジタル - アナログ コンバータ (DAC) を介してエンコードし、メモリ アレイに供給することができることです。

これはソフトウェア シミュレーションではなく、ハードウェアです

CIM アーキテクチャに関する以前の研究はありますが、ソフトウェア シミュレーションではなくハードウェアで広範な AI アプリケーションを実証したのはこれが初めてであり、エネルギー効率が高く、アルゴリズムを正確に実行できます。これは以前の研究のどれにもありません。ワンによると、同時に表示することができました。

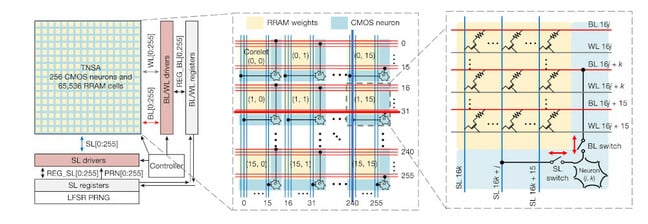

NeuRRAM は、合計 48 万個の RRAM セルを含む 3 個の CIM コアで構成されています。 各コアは、256 × 256 RRAM セルのグリッドと、アナログ デジタル コンバーター (ADC) と活性化機能を実装する 256 の CMOS 人工ニューロン回路で構成される転移可能な神経シナプス アレイ (TNSA) として記述されます。

この論文によると、TNSA アーキテクチャは、データフローの方向を柔軟に制御できるように設計されています。これは、さまざまなデータフロー パターンを持つ多様な AI モデルをサポートするために不可欠です。

たとえば、視覚関連のタスクで一般的な畳み込みニューラル ネットワーク (CNN) では、データはレイヤーを介して一方向に流れ、異なる抽象化レベルでデータ表現を生成しますが、他のモデルでは確率的サンプリングがレイヤー間を行ったり来たりして実行されます。ネットワークが高確率状態に収束するまで。

ただし、CIM と RRAM を組み合わせた他の設計は、通常、RRAM クロスバー アレイの行と列を周辺の専用回路に配線して入力を駆動し、出力を測定することによって、単一方向での動作に制限されていました。

機能

NeuRRAM の再構成可能性の秘訣は、RRAM セル間に CMOS ニューロン回路を分散させ、行と列の両方の長さに沿ってそれらを接続することです。

各 TNSA は多数のコアレットに分割され、各コアレットは 16 × 16 の RRAM セルと XNUMX つのニューロン回路で構成されます。 コアレットは、水平方向に沿って共有ビット線 (BL) とワード線 (WL) によって接続され、垂直方向に沿ってソース線 (SL) によって接続されます。

ニューロン回路は、コアレットを通過する 16 個の BL と SL のうち 256 個の BL と XNUMX 個の SL にスイッチを介して接続し、同じ BL または SL に接続されている XNUMX 個の RRAM すべてからの入力を統合する役割を果たします。

各ニューロン回路は、BL スイッチと SL スイッチを入力と出力に使用できます。 これは、スイッチを介して BL または SL から来る RRAM セルからアナログ行列ベクトル乗算 (MVM) を受信できることを意味しますが、変換されたデジタル結果を同じスイッチを介してペリフェラル レジスタに送信することもできます。

この配置は、各ニューロン回路の入力段階と出力段階でどのスイッチを使用するかを構成することによって、異なるデータフロー方向を実装できることを意味します。

(このアーキテクチャはまた、私たちにいくらか心に留めています SambaNova の AI プロセッサ チップこれは、データフローを制御するオンチップ通信ファブリックによってリンクされた計算ユニットとメモリ ユニットのグリッドとして実装されます。)

論文によると、NeuRRAM の 48 個の CIM コアを使用して AI 推論のパフォーマンスを最大化するために、モデルの並列処理とデータの並列処理の両方を利用するさまざまな重みマッピング戦略を実装することが可能です。

CNN の場合、初期の最も計算集約的なレイヤーの重みを並列推論用の複数の CIM コアに複製するという戦略が考えられます。 このホワイトペーパーでは、使用可能なウェイト マッピング戦略について詳しく説明しています。

この論文では、さまざまな AI モデルで実装された、CIFAR-10 および MNIST データセットを使用した画像分類、Google 音声コマンド認識、MNIST 画像回復など、さまざまな AI タスクにチップを使用して、ハードウェアで測定された推論結果を報告しています。

これらすべてのベンチマーク タスクで 4 ビットの重みでトレーニングされたソフトウェア モデルに匹敵する推論精度を達成すると主張されています。 たとえば、0.98 層 CNN を使用した MNIST 手書き数字認識で 7% のエラー率、ResNet-14.34 を使用した CIFAR-10 オブジェクト分類で 20% のエラー率、Google 音声コマンド認識で 15.34% のエラー率を達成しています。 4 セル LSTM (長期短期記憶)。

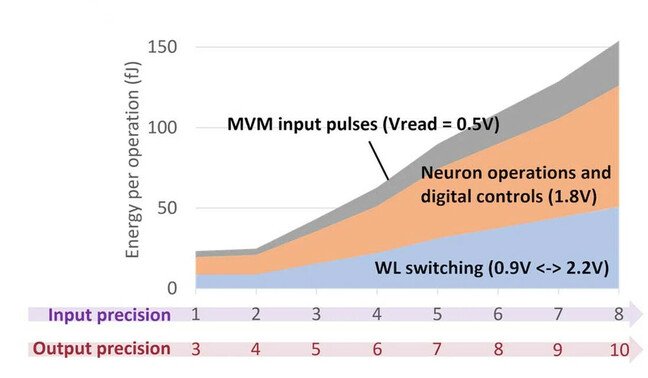

また、NeuRRAM チップは、RRAM を使用した以前の CIM チップ設計よりも、さまざまな計算ビット精度で XNUMX 倍優れたエネルギー効率を持つと主張されています。 ただし、この論文のエネルギー消費量は、市場に出回っている商用デバイスと比較しやすい形で引用されていません。下の図は、フェムトジュール (fJ) で測定されたさまざまなビット精度での動作あたりのエネルギー消費量を示しています。

しかし、Wan 氏によると、現在多くのスマート ホーム デバイスで実行されている典型的なリアルタイム キーワード スポッティング タスク (スマート スピーカーにライトをオンにするように指示するなど) では、NeuRRAM は 2 マイクロワット未満の電力しか消費しないと見積もられています。

「つまり、小型のコイン電池でも、10 年以上動作する可能性があります (他のシステム コンポーネントによって消費される電力を考慮していません)」と彼は言いました。

論文によると、チップは130nm CMOS技術を使用して製造されており、他の半導体製品と同様に、技術のスケーリングに伴ってエネルギー効率が向上することが期待されています。

製品化はまだ数年先

では、この技術に基づいた商用デバイスが出荷されるでしょうか? ワンさんは、商品化の可能性は大いにあると語っており、個人的にも商品化を検討しているとのこと。

「最も適した最初のユースケースは、極端なエッジ/IoT である可能性が非常に高いです」と彼は語った。

NeuRRAM チップに基づく製品は、他のアクセラレータと同様に、CPU を備えたシステムに組み合わせることができますが、これはすべてのアプリケーションに必要というわけではありません。

「最近、センサーからのデータが、CPU や余分なメモリを介さずに AI プロセッサに直接供給される傾向があります」と Wan 氏は述べていますが、実際の展開のほとんどの場合、そのような AI アクセラレータはコプロセッサとして機能すると付け加えました。 CPU の場合、CPU は他のタスクを管理します。

NeuRRAM チップは、推論作業のみを目的としています。これは主に、現在の形式の RRAM テクノロジがトレーニングにあまり適していないためです。トレーニング プロセスではメモリを頻繁に更新する必要があり、これは「RRAM での非常に高価な操作」であると Wan 氏は述べています。

「現在、多くの商用ファウンドリはすでにRRAMデバイスを製造する能力を持っていますが、ほとんどはコンピューティングインメモリではなく、組み込みメモリの用途向けです。 RRAM プロセスが IC 設計者により広く利用できるようになれば、NeuRRAM 製品が実現する可能性があります。」

ただし、これが実現する正確なタイムラインを予測するのは難しく、Wan 氏によると、今後 XNUMX ~ XNUMX 年、あるいはそれ以上かかる可能性があります。 ®