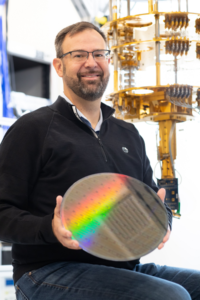

Intel の James Clarke と 300mm シリコン スピン キュービット ウエハー (クレジット: Intel)

インテルは本日、シリコン スピン キュービット デバイスについて、これまでに報告された業界最高の歩留まりと均一性を実証したと発表しました。 「この成果は、Intel のトランジスタ製造プロセスで量子チップを製造するためのスケーリングと取り組みの主要なマイルストーンを表しています」と同社は述べています。

Intel によると、この研究は同社の第 XNUMX 世代シリコン スピン テスト チップを使用して行われたという。 Intel を使用してデバイスをテストする 凍結プローブ極低温 (1.7 ケルビンまたは摂氏 -271.45 度) で動作する量子ドット テスト デバイスで、チームは 12 個の量子ドットと 300 個のセンサーを分離しました。 インテルによると、この結果は、XNUMX mm シリコン ウェーハ全体の各位置に XNUMX つの電子を持つ業界最大のシリコン電子スピン デバイスです。

これらのデバイスは、オレゴン州ヒルズボロのロンラー エイカーズにあるインテルのトランジスタ研究開発施設、ゴードン ムーア パークで開発されました。

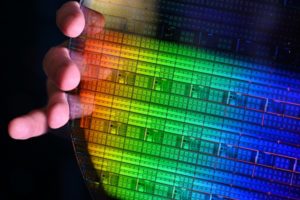

今日のシリコン スピン キュービットは、通常、95 つのデバイスで提供されますが、インテルの研究では、ウェーハ全体での成功が示されています。 極紫外線 (EUV) リソグラフィーを使用して製造されたチップは均一性を示し、ウェーハ全体で 900% の歩留まり率を示します。 クライオプローバーと堅牢なソフトウェア自動化を併用することで、最後の電子で 400 を超える単一量子ドットと 24 を超える二重ドットが可能になり、XNUMX 時間以内に絶対零度より XNUMX 度高い温度で特徴付けることができます。

以前のインテルのテストチップよりも低温で特徴付けられたデバイスの歩留まりと均一性が向上したため、インテルは統計的プロセス制御を使用して、最適化する製造プロセスの領域を特定できると同社は述べています。 これは学習を加速し、商用の量子コンピューターに必要な数千または潜在的に数百万のキュービットにスケーリングするための重要なステップを表しています。

さらに、クロスウェーハ歩留まりにより、インテルは単一電子領域でウェーハ全体のデータ収集を自動化でき、これにより、これまでで最大の単一および二重量子ドットのデモンストレーションが可能になりました。 以前の Intel テスト チップよりも低温で特徴付けられるデバイスのこの増加した歩留まりと均一性は、「商用の量子コンピューターに必要な数千または潜在的に数百万の量子ビットにスケーリングするための重要なステップを表しています」と同社は述べています。

Intel の 30mm シリコン スピン キュービット ウエハー (クレジット: Intel)

Intel の量子ハードウェア担当ディレクターである James Clarke は、次のように述べています。 「達成された高い歩留まりと均一性は、Intel の確立されたトランジスタ プロセス ノード上で量子チップを製造することが適切な戦略であり、技術が商業化に向けて成熟するにつれて成功するための強力な指標であることを示しています。」

「将来的には、これらのデバイスの品質を向上させ、大規模なシステムを開発し続けます。これらのステップは、私たちが迅速に前進するための構成要素として機能します」とクラークは言いました。