더 큰 AI 및 기계 학습 모델에 대한 갈증을 해소하기 위해 Tesla는 Hot Chips 34에서 Dojo라는 완전 맞춤형 슈퍼컴퓨팅 아키텍처에 대한 풍부한 세부 정보를 공개했습니다.

시스템은 기본적으로 구성 가능한 거대한 슈퍼컴퓨터이지만, 최고 500, 컴퓨팅, 네트워킹 및 I/O(입/출력) 실리콘에서 ISA(명령 세트 아키텍처), 전원 공급, 패키징 및 냉각에 이르는 완전히 맞춤형 아키텍처로 구축되었습니다. 이 모든 것은 맞춤형 특정 머신 러닝 훈련 알고리즘을 대규모로 실행하려는 명백한 목적으로 수행되었습니다.

Tesla의 하드웨어 엔지니어링 수석 이사인 Ganesh Venkataramanan은 "실제 데이터 처리는 기계 학습 기술을 통해서만 실현 가능합니다. 자연어 처리, 인간의 시각을 위해 만들어진 거리에서의 운전, 로봇이 일상적인 환경과 상호작용하는 것"이라고 말했습니다. 그의 기조연설 중.

그러나 그는 분산 워크로드를 확장하는 기존 방법이 머신 러닝의 요구 사항을 따라가는 데 필요한 속도로 가속화하지 못했다고 주장했습니다. 실제로 무어의 법칙은 이를 줄이지 않으며 CPU/GPU의 일부 조합 또는 드물게 특수 AI 가속기를 사용하여 대규모 AI/ML 교육에 사용할 수 있는 시스템도 없습니다.

“전통적으로 우리는 칩을 만들고 패키지에 넣고 패키지는 시스템에 들어가는 PCB에 넣습니다. 시스템은 랙에 들어갑니다.”라고 Venkataramanan은 말했습니다. 문제는 데이터가 칩에서 패키지로 그리고 패키지 밖으로 이동할 때마다 대기 시간과 대역폭 페널티가 발생한다는 것입니다.

데이터 센터 샌드위치

그래서 한계를 극복하기 위해 Venkataramanan과 그의 팀은 처음부터 다시 시작했습니다.

“Elon과의 인터뷰에서 그는 나에게 AI용 CPU 및 GPU와 다른 점이 무엇인지 물었습니다. 팀 전체가 여전히 그 질문에 답하고 있다고 생각합니다.”

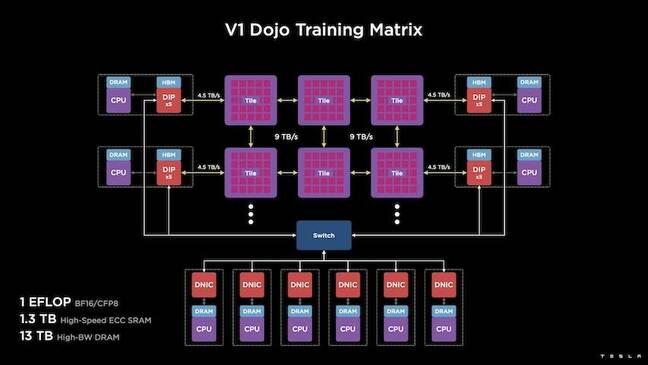

이로 인해 556kW 수냉식 패키지에서 FP32 성능의 15TFLOPS를 처리할 수 있는 반 입방 피트를 차지하는 독립형 컴퓨팅 클러스터인 Dojo 교육 타일이 개발되었습니다.

각 타일에는 11GB의 SRAM이 장착되어 있으며 전체 스택에서 맞춤형 전송 프로토콜을 사용하여 9TB/s 패브릭을 통해 연결됩니다.

Venkataramanan은 "이 교육 타일은 컴퓨터에서 메모리, 전원 공급, 통신에 이르기까지 추가 스위치 없이 통합할 수 있는 비할 데 없는 양을 나타냅니다."라고 말했습니다.

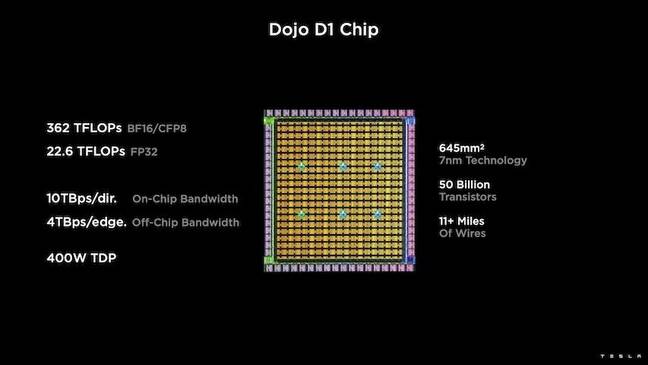

훈련 타일의 핵심은 TSMC의 1nm 공정을 기반으로 하는 50억 개의 트랜지스터 다이인 Tesla의 D7입니다. Tesla는 각 D1이 22W의 TDP에서 32TFLOPS의 FP400 성능을 낼 수 있다고 말합니다. 그러나 Tesla는 이 칩이 몇 가지 맞춤형 계산을 포함하여 광범위한 부동 소수점 계산을 실행할 수 있다고 말합니다.

Venkataramanan은 "트랜지스터를 밀리미터 제곱으로 비교한다면 이것은 아마도 현존하는 모든 것의 최첨단일 것입니다."라고 말했습니다.

Tesla는 그런 다음 25개의 D1을 가져와서 양호한 다이로 분류한 다음 TSMC의 시스템 온 웨이퍼 기술을 사용하여 패키징하여 "매우 짧은 대기 시간과 매우 높은 대역폭에서 엄청난 양의 컴퓨팅 통합을 달성"했다고 말했습니다.

그러나 시스템-온-웨이퍼 설계와 수직 스택 아키텍처는 전력 공급과 관련하여 문제를 야기했습니다.

Venkataramanan에 따르면 오늘날 대부분의 가속기는 전력을 실리콘에 직접 인접하게 배치합니다. 그리고 입증되었지만 이 접근 방식은 가속기의 넓은 영역이 이러한 구성 요소에 전용되어야 한다는 것을 의미하므로 Dojo에서는 비실용적이라고 그는 설명했습니다. 대신 Tesla는 칩을 다이 바닥을 통해 직접 전력을 공급하도록 설계했습니다.

함께 모아서

“이 교육 타일로 전체 데이터 센터 또는 전체 건물을 구축할 수 있지만 교육 타일은 컴퓨팅 부분일 뿐입니다. 우리도 먹이를 주어야 합니다.”라고 Venkataramanan이 말했습니다.

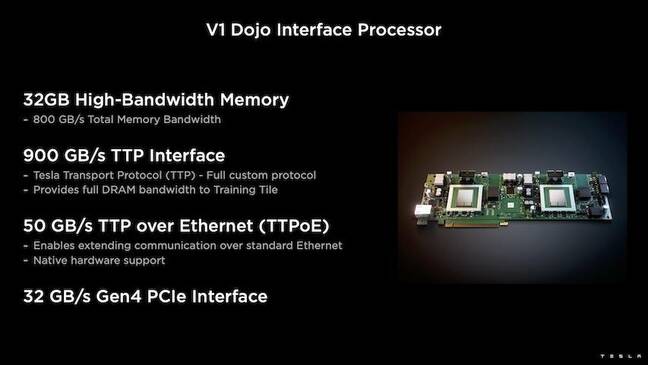

이를 위해 Tesla는 호스트 CPU와 교육 프로세서 간의 다리 역할을 하는 DIP(Dojo Interface Processor)도 개발했습니다. DIP는 또한 공유 고대역폭 메모리(HBM)의 소스 및 고속 400Gbit/sec NIC의 역할도 합니다.

각 DIP는 32GB의 HBM을 제공하며 최대 900개의 이러한 카드를 4.5GB/s의 속도로 교육 타일에 연결하여 타일당 총 160GB의 HBM에 대해 호스트에 총 XNUMXTB/s를 연결할 수 있습니다.

이 타일의 Tesla V1 구성 쌍(또는 150개의 D1 다이)은 각각 16개의 DIP 카드가 장착된 8개의 호스트 CPU를 지원하여 BFXNUMX 또는 CFPXNUMX 성능의 엑사플롭을 달성했습니다.

종합하여 Venkataramanan은 아키텍처를 말합니다. 깊이 여기 by 다음 플랫폼 – Tesla는 Nvidia 및 AMD와 같은 기존 가속기와 관련된 한계를 극복할 수 있습니다.

“기존 가속기의 작동 방식, 일반적으로 전체 모델을 각 가속기에 맞추려고 합니다. 복제한 다음 각각을 통해 데이터를 흘려보냅니다.”라고 그는 말했습니다. "더 큰 모델이 있으면 어떻게 될까요? 이러한 가속기는 메모리가 부족하여 고장날 수 있습니다."

이것은 새로운 문제가 아니라고 그는 지적했다. 예를 들어 Nvidia의 NV 스위치를 사용하면 대규모 GPU 뱅크에서 메모리를 풀링할 수 있습니다. 그러나 Venkataramanan은 이것이 복잡성을 추가할 뿐만 아니라 대기 시간과 대역폭 타협을 초래한다고 주장합니다.

“우리는 처음부터 이것에 대해 생각했습니다. 우리의 컴퓨팅 타일과 각 다이는 대형 모델에 맞게 제작되었습니다.”라고 Venkataramanan이 말했습니다.

소프트웨어

이러한 특수 컴퓨팅 아키텍처에는 특수 소프트웨어 스택이 필요합니다. 그러나 Venkataramanan과 그의 팀은 프로그래밍 가능성이 Dojo를 만들거나 깨뜨릴 것임을 인식했습니다.

“소프트웨어 대응을 위한 프로그래밍 용이성은 우리가 이러한 시스템을 설계할 때 가장 중요합니다.”라고 그는 말했습니다. "연구원들은 소프트웨어 사람들이 우리가 실행하려는 새로운 알고리즘에 적응하기 위해 손으로 쓴 커널을 작성하기를 기다리지 않을 것입니다."

이를 위해 Tesla는 커널 사용에 대한 아이디어를 버리고 컴파일러를 중심으로 Dojo의 아키텍처를 설계했습니다.

“우리가 한 것은 PiTorch를 사용한 것입니다. 우리는 그 아래에 있는 하드웨어를 확장하기 위해 병렬화하는 데 도움이 되는 중간 계층을 만들었습니다. 모든 것 아래에는 컴파일된 코드가 있습니다.”라고 그는 말했습니다. "이것이 미래의 모든 워크로드에 적응할 수 있는 소프트웨어 스택을 생성하는 유일한 방법입니다."

소프트웨어 유연성에 대한 강조에도 불구하고 Venkataramanan은 현재 그들의 연구실에서 실행 중인 플랫폼이 당분간 Tesla 사용으로 제한된다는 점에 주목합니다.

“우리는 먼저 내부 고객에 초점을 맞추고 있습니다.”라고 그는 말했습니다. “Elon은 시간이 지남에 따라 우리가 이것을 연구원들이 사용할 수 있도록 공개할 것이지만, 우리는 그것에 대한 일정이 없습니다. ®