Een nieuw gepubliceerd onderzoeksartikel beschrijft een compute-in-memory (CIM) -chip die kunstmatige neuronen combineert met resistief RAM (RRAM), zodat de AI-modelgewichten op dezelfde chip kunnen worden opgeslagen en verwerkt.

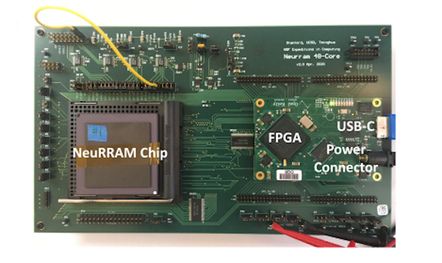

Een compute-in-memory-chip op basis van resistief willekeurig toegankelijk geheugen (klik om te vergroten). Afbeelding: Wan et al

Onderzoekers achter het ontwerp beweren dat het efficiënter zou zijn voor edge-applicaties omdat het gegevensverplaatsing tussen afzonderlijke reken- en geheugenblokken elimineert.

Edge computing en kunstmatige intelligentie liggen beide op schema voor snelle groei in de nabije toekomst, tenminste volgens analistenbedrijf IDC. Sommige scenario's combineren ze met elkaar omdat edge-implementaties mogelijk beperkt zijn in stroom en connectiviteit, maar toch aanzienlijke hoeveelheden gegevens moeten analyseren en een bijna realtime reactie op gebeurtenissen moeten leveren, waardoor een AI-model dat in het apparaat "leeft" de meest optimale oplossing is .

In het licht hiervan heeft een groep onderzoekers een chip ontwikkeld die het NeuRRAM noemt, omdat het kunstmatige neuronen combineert met RRAM in een nieuwe architectuur. Het doel van het project was om een ontwerp te leveren dat tegelijkertijd een hoge energie-efficiëntie kan bieden, evenals de veelzijdigheid om verschillende AI-modellen te ondersteunen, en een vergelijkbare nauwkeurigheid als het draaien van hetzelfde model in software.

Het project begon in eerste instantie als onderdeel van een Nature Science Foundation-project genaamd "Expeditions in Computing". Dit project bracht een groep onderzoekers samen van verschillende instellingen met verschillende achtergronden, waaronder enkele van Stanford en UCSD, evenals onderzoekers van de Tsinghua University in China die experts zijn in de fabricage van RRAM-apparaten.

Energie-efficiëntie: AI-inferentie gedaan op de batterijgevoede gizmo

Volgens Weier Wan, een afgestudeerde onderzoeker aan de Stanford University en een van de auteurs van de krant, gisteren gepubliceerd in Nature, is NeuRRAM ontwikkeld als een AI-chip die de energie-efficiëntie van AI-inferentie aanzienlijk verbetert, waardoor complexe AI-functies direct kunnen worden gerealiseerd in randapparatuur op batterijen, zoals slimme wearables, drones en industriële IoT-sensoren .

“In de huidige AI-chips vinden gegevensverwerking en gegevensopslag op verschillende plaatsen plaats: rekeneenheid en geheugeneenheid. De frequente gegevensbeweging tussen deze eenheden verbruikt de meeste energie en wordt de bottleneck voor het realiseren van low-power AI-processors voor edge-apparaten, "zei hij.

Om dit aan te pakken, implementeert de NeuRRAM-chip een "compute-in-memory" -model, waarbij de verwerking rechtstreeks in het geheugen plaatsvindt. Het maakt ook gebruik van resistief RAM (RRAM), een geheugentype dat net zo snel is als statisch RAM, maar niet-vluchtig is, waardoor het AI-modelgewichten kan opslaan. Een belangrijk kenmerk van RRAM-cellen is dat neurale gewichten in geheugencellen kunnen worden opgeslagen als verschillende geleidingsniveaus, gecodeerd via digitaal-naar-analoogomzetters (DAC's) en naar de geheugenarray kunnen worden gevoerd.

Dit is geen softwaresimulatie, het is hardware

Er zijn eerdere onderzoeken geweest naar CIM-architecturen, maar dit is de eerste die een breed scala aan AI-toepassingen in hardware demonstreert in plaats van in softwaresimulatie, terwijl het energiezuiniger is en de algoritmen nauwkeurig kan uitvoeren, iets wat geen van de eerdere onderzoeken tegelijk konden laten zien, aldus Wan.

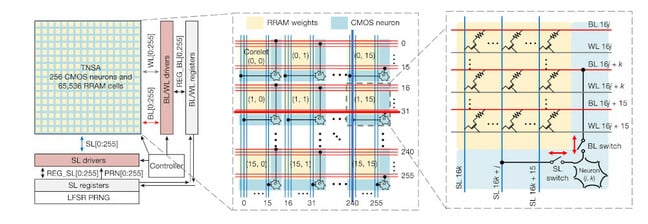

De NeuRRAM bestaat uit 48 CIM-cores met in totaal 3 miljoen RRAM-cellen. Elke kern wordt beschreven als een transponeerbare neurosynaptische array (TNSA) bestaande uit een raster van 256 × 256 RRAM-cellen en 256 CMOS kunstmatige neuroncircuits die analoog-naar-digitaal-omzetters (ADC's) en activeringsfuncties implementeren.

Volgens het artikel is de TNSA-architectuur ontworpen om flexibele controle te bieden over de richting van gegevensstromen, wat cruciaal is voor het ondersteunen van een breed scala aan AI-modellen met verschillende gegevensstroompatronen.

In convolutionele neurale netwerken (CNN's) die gebruikelijk zijn in visiegerelateerde taken, stromen gegevens bijvoorbeeld in één richting door lagen om gegevensrepresentaties op verschillende abstractieniveaus te genereren, terwijl in sommige andere modellen probabilistische bemonstering heen en weer wordt uitgevoerd tussen lagen totdat het netwerk convergeert naar een toestand met hoge waarschijnlijkheid.

Andere ontwerpen die CIM met RRAM hebben gecombineerd, waren echter beperkt tot het werken in een enkele richting, meestal door rijen en kolommen van de RRAM-dwarsbalkarray vast te bedraden naar speciale circuits aan de periferie om inputs aan te sturen en outputs te meten, zegt de krant.

Hoe het werkt

Het geheim van de herconfigureerbare NeuRRAM is dat het de CMOS-neuroncircuits verdeelt over de RRAM-cellen en ze verbindt langs de lengte van zowel rijen als kolommen.

Elke TNSA is onderverdeeld in een aantal corelets, die elk bestaan uit 16 × 16 RRAM-cellen en één neuroncircuit. De corelets zijn verbonden door gedeelde bitlijnen (BL's) en woordlijnen (WL's) langs de horizontale richting, en bronlijnen (SL's) langs de verticale richting.

Het neuroncircuit is via schakelaars verbonden met één BL en één SL van de 16 van elk die door de corelet gaan, en is verantwoordelijk voor het integreren van ingangen van alle 256 RRAM's die op dezelfde BL of SL zijn aangesloten.

Elk neuroncircuit kan zijn BL- en SL-schakelaars gebruiken voor invoer en uitvoer. Dit betekent dat het de analoge matrix-vectorvermenigvuldiging (MVM) kan ontvangen van een RRAM-cel afkomstig van BL of SL via de schakelaars, maar ook de geconverteerde digitale resultaten naar perifere registers kan sturen via dezelfde schakelaars.

Deze opstelling betekent dat verschillende gegevensstroomrichtingen kunnen worden geïmplementeerd door te configureren welke schakelaar moet worden gebruikt tijdens de invoer- en uitvoerfasen van elk neuroncircuit.

(Deze architectuur doet ons ook enigszins denken aan) SambaNova's AI-processorchip, die is geïmplementeerd als een raster van rekeneenheden en geheugeneenheden, verbonden door een on-chip communicatiestructuur die de gegevensstroom bestuurt.)

Om de AI-inferentieprestaties te maximaliseren met behulp van de 48 CIM-kernen in de NeuRRAM, is het volgens het artikel mogelijk om verschillende strategieën voor gewichtstoewijzing te implementeren die zowel modelparallellisme als gegevensparallellisme benutten.

In het geval van een CNN kan de strategie zijn om de gewichten van de vroege, meest rekenintensieve lagen te dupliceren naar meerdere CIM-kernen voor parallelle inferentie. Het artikel geeft een meer gedetailleerde beschrijving van de beschikbare strategieën voor het in kaart brengen van gewicht.

De paper rapporteert hardware-gemeten inferentieresultaten met behulp van de chip voor een reeks AI-taken, waaronder beeldclassificaties met behulp van CIFAR-10- en MNIST-datasets, herkenning van spraakopdrachten van Google en MNIST-beeldherstel, geïmplementeerd met verschillende AI-modellen.

Er wordt beweerd dat de inferentienauwkeurigheid vergelijkbaar is met softwaremodellen die zijn getraind met 4-bits gewichten voor al deze benchmarktaken. Het behaalt bijvoorbeeld een foutenpercentage van 0.98 procent op MNIST handgeschreven cijferherkenning met behulp van een 7-laags CNN, een foutenpercentage van 14.34 procent op CIFAR-10 objectclassificatie met behulp van ResNet-20 en een foutenpercentage van 15.34 procent op Google spraakopdrachtherkenning met behulp van een 4-cell LSTM (lange korte termijn geheugen).

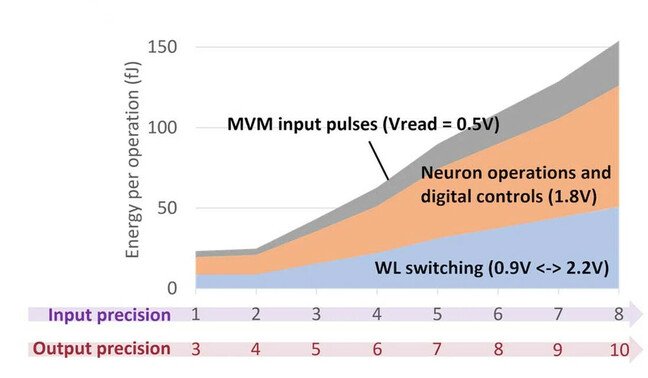

Er wordt ook beweerd dat de NeuRRAM-chip een energie-efficiëntie heeft die twee keer beter is dan eerdere CIM-chipontwerpen die RRAM gebruiken, over verschillende computationele bitnauwkeurigheden. Het energieverbruik in de krant wordt echter niet vermeld in een vorm die gemakkelijk te vergelijken is met commerciële apparaten op de markt, en de onderstaande afbeelding illustreert het energieverbruik per bewerking in verschillende bitnauwkeurigheden gemeten in femtojoules (fJ).

Wan vertelde ons echter dat voor een typische realtime taak voor het spotten van trefwoorden die tegenwoordig op veel slimme apparaten voor thuisgebruik wordt uitgevoerd (zoals een slimme luidspreker vertellen om het licht aan te doen), NeuRRAM naar schatting minder dan 2 microwatt aan stroom verbruikt.

"Dat betekent dat hij zelfs op een kleine knoopbatterij meer dan 10 jaar kan werken (afgezien van het stroomverbruik van andere systeemcomponenten)", zei hij.

Volgens de krant is de chip gefabriceerd met behulp van een 130nm CMOS-technologie, en de verwachting is dat de energie-efficiëntie zal verbeteren met de technologische schaalvergroting, zoals het geval is voor andere halfgeleiderproducten.

Productie nog jaren weg

Dus zullen we een commercieel apparaat zien dat op deze technologie is gebaseerd? Wan zegt dat het een groot potentieel heeft om te worden gecommercialiseerd en overweegt persoonlijk om het zelf te gaan produceren.

"De meest geschikte eerste use-case is zeer waarschijnlijk in extreme edge / IoT", vertelde hij ons.

Een product op basis van de NeuRRAM-chip kan in een systeem worden gecombineerd met een CPU, zoals bij andere versnellers, maar dit is niet voor elke toepassing nodig.

"Onlangs is er een trend geweest waarbij gegevens van sensoren rechtstreeks naar AI-processors worden gevoerd zonder door CPU of extra geheugen te gaan", zei Wan, maar hij voegde eraan toe dat dergelijke AI-versnellers voor de meeste gevallen van echte implementatie fungeren als een co-processor voor een CPU, waar de CPU andere taken beheert.

De NeuRRAM-chip is alleen bedoeld voor het afleiden van werk, grotendeels omdat de RRAM-technologie in zijn huidige vorm niet erg geschikt is voor training, omdat het trainingsproces frequente updates van het geheugen vereist, en dit is "een zeer dure operatie op RRAM", zei Wan.

“Momenteel hebben veel commerciële gieterijen al de mogelijkheid om RRAM-apparaten te fabriceren, maar meestal voor embedded geheugengebruik in plaats van voor compute-in-memory. Zodra het RRAM-proces breder beschikbaar komt voor IC-ontwerpers, zou een NeuRRAM-product kunnen ontstaan.

De exacte tijdlijn hiervoor is echter moeilijk te voorspellen, en Wan zei dat dit in de komende twee tot drie jaar zou kunnen zijn, of veel langer. ®

- AI

- ai kunst

- ai kunst generator

- je hebt een robot

- kunstmatige intelligentie

- certificering van kunstmatige intelligentie

- kunstmatige intelligentie in het bankwezen

- kunstmatige intelligentie robot

- kunstmatige intelligentie robots

- kunstmatige intelligentiesoftware

- blockchain

- blockchain conferentie ai

- vindingrijk

- conversatie kunstmatige intelligentie

- crypto conferentie ai

- van dall

- diepgaand leren

- google ai

- machine learning

- Plato

- plato ai

- Plato gegevensintelligentie

- Plato-spel

- PlatoData

- platogamen

- schaal ai

- syntaxis

- Het register

- zephyrnet