Niedawno opublikowany artykuł badawczy opisuje układ obliczeniowy w pamięci (CIM), który łączy sztuczne neurony z rezystancyjną pamięcią RAM (RRAM), dzięki czemu wagi modelu AI mogą być przechowywane i przetwarzane na tym samym układzie.

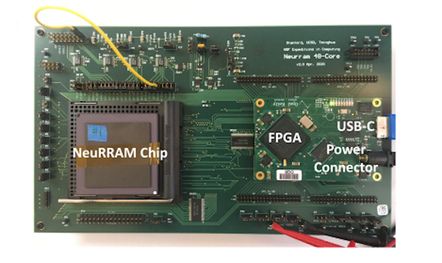

Układ obliczeniowy w pamięci oparty na rezystancyjnej pamięci o dostępie swobodnym (kliknij, aby powiększyć). Zdjęcie: Wan i inni

Badacze stojący za projektem twierdzą, że byłby on bardziej wydajny w przypadku aplikacji brzegowych, ponieważ eliminuje przenoszenie danych między oddzielnymi blokami obliczeniowymi i pamięciowymi.

Edge computing i sztuczna inteligencja są na dobrej drodze do błyskawicznego wzrostu przynajmniej w najbliższej przyszłości według firmy analitycznej IDC. Niektóre scenariusze łączą je ze sobą, ponieważ wdrożenia brzegowe mogą być ograniczone mocą i łącznością, ale nadal muszą analizować znaczne ilości danych i zapewniać reakcję na zdarzenia w czasie zbliżonym do rzeczywistego, co sprawia, że model AI „żyjący” w urządzeniu jest najbardziej optymalnym rozwiązaniem .

W związku z tym grupa naukowców opracowała chip, który nazywa NeuRRAM, ponieważ łączy on sztuczne neurony z RRAM w nowatorskiej architekturze. Celem projektu było dostarczenie projektu, który może jednocześnie zapewnić wysoką wydajność energetyczną, a także wszechstronność obsługi różnych modeli sztucznej inteligencji i porównywalną dokładność do uruchamiania tego samego modelu w oprogramowaniu.

Projekt początkowo rozpoczął się w ramach projektu Nature Science Foundation o nazwie „Ekspedycje w informatyce”. Projekt ten zgromadził grupę naukowców z różnych instytucji o różnym wykształceniu, w tym niektórych ze Stanford i UCSD, a także naukowców z Uniwersytetu Tsinghua w Chinach, którzy są ekspertami w produkcji urządzeń RRAM.

Efektywność energetyczna: wnioskowanie AI wykonane na gadżetach zasilanych bateryjnie

Według Weiera Wana, absolwenta naukowca na Uniwersytecie Stanforda i jednego z autorzy artykułu, opublikowanym wczoraj w Nature, NeuRRAM został opracowany jako chip AI, który znacznie poprawia efektywność energetyczną wnioskowania AI, umożliwiając w ten sposób realizację złożonych funkcji AI bezpośrednio w urządzeniach brzegowych zasilanych bateryjnie, takich jak inteligentne urządzenia do noszenia, drony i przemysłowe czujniki IoT .

„W dzisiejszych chipach AI przetwarzanie i przechowywanie danych odbywa się w oddzielnych miejscach – jednostce obliczeniowej i jednostce pamięci. Częsty przepływ danych między tymi jednostkami pochłania najwięcej energii i staje się wąskim gardłem w realizacji niskoenergetycznych procesorów AI dla urządzeń brzegowych” – powiedział.

Aby rozwiązać ten problem, chip NeuRRAM implementuje model „obliczenia w pamięci”, w którym przetwarzanie odbywa się bezpośrednio w pamięci. Wykorzystuje również rezystancyjną pamięć RAM (RRAM), typ pamięci, który jest tak szybki jak statyczna pamięć RAM, ale jest nieulotny, co pozwala na przechowywanie wag modeli AI. Kluczową cechą komórek RRAM jest to, że wagi neuronowe mogą być przechowywane w komórkach pamięci jako różne poziomy przewodnictwa, kodowane przez przetworniki cyfrowo-analogowe (DAC) i podawane do macierzy pamięci.

To nie jest symulacja oprogramowania, to sprzęt

Przeprowadzono wcześniejsze badania dotyczące architektur CIM, ale jest to pierwsze, które zademonstrowało szeroki zakres zastosowań sztucznej inteligencji w sprzęcie, a nie w symulacji oprogramowania, a jednocześnie jest bardziej energooszczędny i zdolny do dokładnego uruchamiania algorytmów, czego nie było w poprzednich badaniach byli w stanie pokazać jednocześnie, zgodnie z Wan.

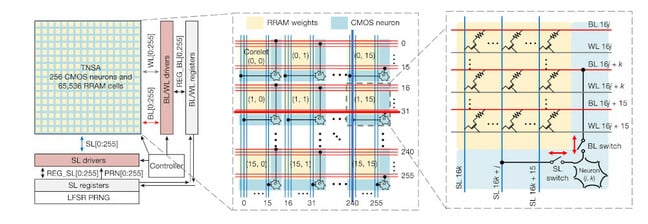

NeuRRAM składa się z 48 rdzeni CIM składających się w sumie z 3 milionów komórek RRAM. Każdy rdzeń jest opisany jako transpozycyjna macierz neurosynaptyczna (TNSA) składająca się z siatki 256 × 256 komórek RRAM i 256 sztucznych obwodów neuronowych CMOS, które implementują przetworniki analogowo-cyfrowe (ADC) i funkcje aktywacji.

Według artykułu architektura TNSA została zaprojektowana tak, aby oferować elastyczną kontrolę kierunku przepływu danych, co ma kluczowe znaczenie dla obsługi zróżnicowanej gamy modeli AI o różnych wzorcach przepływu danych.

Na przykład w splotowych sieciach neuronowych (CNN), które są powszechne w zadaniach związanych z wizją, dane przepływają w jednym kierunku przez warstwy, aby wygenerować reprezentacje danych na różnych poziomach abstrakcji, podczas gdy w niektórych innych modelach próbkowanie probabilistyczne jest przeprowadzane tam i z powrotem między warstwami dopóki sieć nie osiągnie stanu wysokiego prawdopodobieństwa.

Jednak inne projekty, które łączyły CIM z pamięcią RRAM, były ograniczone do działania w jednym kierunku, zwykle przez okablowanie rzędów i kolumn tablicy poprzecznej pamięci RAM z dedykowanymi obwodami na peryferiach, aby sterować wejściami i mierzyć wyjścia, czytamy w artykule.

Jak to działa?

Sekret rekonfigurowalności NeuRRAM polega na tym, że rozdziela on obwody neuronów CMOS pomiędzy komórki RRAM i łączy je wzdłuż zarówno rzędów, jak i kolumn.

Każdy TNSA jest podzielony na szereg rdzeni, z których każdy składa się z 16 × 16 komórek RRAM i jednego obwodu neuronowego. Corelety są połączone wspólnymi liniami bitowymi (BL) i liniami słów (WL) wzdłuż kierunku poziomego oraz liniami źródłowymi (SL) wzdłuż kierunku pionowego.

Obwód neuronowy łączy się za pomocą przełączników z jednym BL i jednym SL z 16 każdego z nich, które przechodzi przez corelet, i jest odpowiedzialny za integrację danych wejściowych ze wszystkich 256 pamięci RRAM łączących się z tym samym BL lub SL.

Każdy obwód neuronowy może używać swoich przełączników BL i SL jako wejścia i wyjścia. Oznacza to, że może odbierać analogowe mnożenie wektora macierzy (MVM) z komórki RRAM pochodzącej z BL lub SL za pośrednictwem przełączników, ale może również wysyłać przekonwertowane wyniki cyfrowe do rejestrów peryferyjnych za pośrednictwem tych samych przełączników.

Ten układ oznacza, że różne kierunki przepływu danych można zaimplementować, konfigurując, który przełącznik ma być używany podczas etapów wejściowych i wyjściowych każdego obwodu neuronowego.

(Ta architektura również przypomina nam nieco Układ procesora AI SambaNova, który jest zaimplementowany jako siatka jednostek obliczeniowych i jednostek pamięci połączonych za pomocą wbudowanej sieci szkieletowej, która steruje przepływem danych).

Zgodnie z artykułem, aby zmaksymalizować wydajność wnioskowania AI przy użyciu 48 rdzeni CIM w NeuRRAM, możliwe jest wdrożenie różnych strategii mapowania wag, które wykorzystują zarówno równoległość modelu, jak i równoległość danych.

W przypadku CNN strategią może być powielanie wag wczesnych, najbardziej intensywnych obliczeniowo warstw do wielu rdzeni CIM w celu równoległego wnioskowania. Artykuł zawiera bardziej szczegółowy opis dostępnych strategii mapowania wag.

Artykuł przedstawia wyniki wnioskowania mierzone sprzętowo przy użyciu chipa do szeregu zadań AI, w tym klasyfikacji obrazów przy użyciu zestawów danych CIFAR-10 i MNIST, rozpoznawania poleceń mowy Google i odzyskiwania obrazu MNIST, zaimplementowanych z różnymi modelami AI.

Twierdzi się, że osiąga dokładność wnioskowania porównywalną z modelami oprogramowania wyszkolonymi z 4-bitowymi wagami we wszystkich tych zadaniach porównawczych. Na przykład, osiąga wskaźnik błędów 0.98 procent w rozpoznawaniu odręcznych cyfr MNIST przy użyciu 7-warstwowej CNN, wskaźnik błędów 14.34 procent w klasyfikacji obiektów CIFAR-10 przy użyciu ResNet-20 i wskaźnik błędów 15.34 procent w rozpoznawaniu poleceń głosowych Google przy użyciu 4-komorowy LSTM (długa pamięć krótkotrwała).

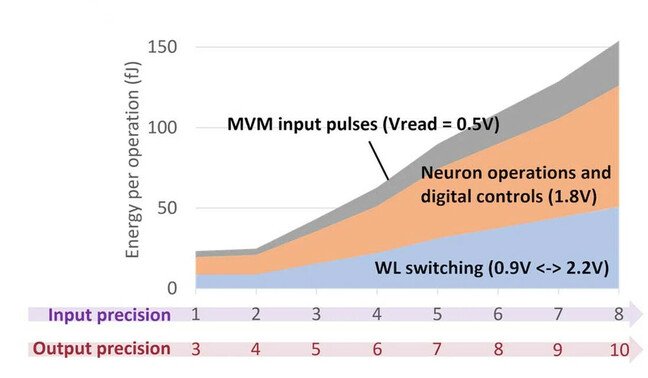

Twierdzi się również, że układ NeuRRAM ma dwukrotnie wyższą wydajność energetyczną niż wcześniejsze projekty układów CIM wykorzystujące pamięć RRAM, przy różnych dokładnościach obliczeniowych bitów. Jednak zużycie energii w artykule nie jest podane w formie łatwej do porównania z komercyjnymi urządzeniami dostępnymi na rynku, a poniższy rysunek ilustruje zużycie energii na operację przy różnych dokładnościach bitowych mierzonych w femtodżulach (fJ).

Jednak Wan powiedział nam, że w przypadku typowego zadania wykrywania słów kluczowych w czasie rzeczywistym, które działa obecnie na wielu inteligentnych urządzeniach domowych (takich jak polecenie inteligentnego głośnika, aby włączył światło), szacuje się, że NeuRRAM zużywa mniej niż 2 mikrowaty energii.

„Oznacza to, że nawet na małej baterii pastylkowej może działać przez ponad 10 lat (nie biorąc pod uwagę energii zużywanej przez inne komponenty systemu)” – powiedział.

Według artykułu, chip jest wytwarzany w technologii 130 nm CMOS i oczekuje się, że wydajność energetyczna poprawi się wraz ze skalowaniem technologii, tak jak w przypadku innych produktów półprzewodnikowych.

Jeszcze lata do produkcji

Czy zatem zobaczymy komercyjne urządzenie do wysyłki oparte na tej technologii? Wan mówi, że ma ogromny potencjał do komercjalizacji i osobiście rozważa pracę nad jego produkcją.

„Najbardziej odpowiedni początkowy przypadek użycia jest bardzo prawdopodobny w skrajnej krawędzi / IoT” – powiedział nam.

Produkt oparty na chipie NeuRRAM mógłby być połączony w systemie z procesorem, podobnie jak inne akceleratory, ale nie jest to konieczne dla każdej aplikacji.

„Ostatnio pojawił się trend polegający na tym, że dane z czujników są bezpośrednio przesyłane do procesorów AI bez przechodzenia przez procesor lub dodatkową pamięć”, powiedział Wan, ale dodał, że w większości przypadków wdrożeń w świecie rzeczywistym takie akceleratory AI działają jako koprocesor dla CPU, gdzie CPU zarządza innymi zadaniami.

Chip NeuRRAM jest przeznaczony wyłącznie do wnioskowania o pracy, głównie dlatego, że technologia RRAM w obecnej formie nie jest zbyt odpowiednia do trenowania, ponieważ proces uczenia wymaga częstych aktualizacji pamięci, a jest to „bardzo kosztowna operacja na RRAM”, powiedział Wan.

„Obecnie wiele komercyjnych odlewni ma już możliwość wytwarzania urządzeń RRAM, ale głównie do zastosowań w pamięci wbudowanej, a nie do obliczeń w pamięci. Gdy proces RRAM stanie się szerzej dostępny dla projektantów układów scalonych, może powstać produkt NeuRRAM”.

Trudno jednak przewidzieć dokładny harmonogram, a Wan powiedział, że może to nastąpić w ciągu najbliższych dwóch do trzech lat lub znacznie dłużej. ®

- AI

- ai sztuka

- generator sztuki ai

- masz robota

- sztuczna inteligencja

- certyfikacja sztucznej inteligencji

- sztuczna inteligencja w bankowości

- robot sztucznej inteligencji

- roboty sztucznej inteligencji

- oprogramowanie sztucznej inteligencji

- blockchain

- konferencja blockchain ai

- pomysłowość

- sztuczna inteligencja konwersacyjna

- konferencja kryptograficzna

- Dall's

- głęboka nauka

- google to

- uczenie maszynowe

- plato

- Platon Ai

- Analiza danych Platona

- Gra Platona

- PlatoDane

- platogaming

- skala ai

- składnia

- Rejestr

- zefirnet