Oto BWAIN w tym tygodniu, nasz żartobliwy termin na Błąd o imponującej nazwie.

BWAIN to wyróżnienie, które wręczamy, gdy nowa luka w cyberbezpieczeństwie nie tylko okazuje się interesująca i ważna, ale także pojawia się z własnym logo, nazwą domeny i stroną internetową.

Ten jest dubbingowany ÆWyciek PIC, kalambur na słowach APIC i EPICKI.

Ten pierwszy jest skrótem od Zaawansowany programowalny kontroler przerwań, a to ostatnie to po prostu słowo „epicki”, jak w gigant, masywny, skrajny, mega, gigantyczny.

Litera Æ nie była używana w pisanym języku angielskim od czasów saskich. Jego nazwa to escwymawiane jesion (jak w drzewie) i w dużym stopniu reprezentuje dźwięk litery A we współczesnym słowie ASH. Ale zakładamy, że powinieneś wymówić to słowo ĆPIK tutaj albo jako „APIC-slash-EPIC”, albo jako „ah!-eh?-PIC”.

O czym to jest?

Wszystko to rodzi pięć fascynujących pytań:

- Co to jest APICi dlaczego go potrzebuję?

- Jak możesz mieć dane, które? nawet jądro nie możesz zajrzeć?

- Co powoduje tę epicką porażkę w APIC?

- Czy ÆWyciek PIC wpływa na mnie?

- Co zrobić o tym?

Co to jest APIC?

Cofnijmy się do 1981 roku, kiedy pojawił się IBM PC.

Komputer zawiera układ o nazwie Programowalny kontroler przerwań Intel 8259Alub PIC. (Późniejsze modele, począwszy od PC AT, miały dwa PIC połączone ze sobą, aby obsługiwać więcej zdarzeń przerwań.)

Celem PIC było dosłownie przerwanie programu działającego na centralnym procesorze (CPU) komputera, gdy wydarzyło się coś krytycznego czasowo, co wymagało natychmiastowej uwagi.

Te przerwania sprzętowe obejmowały zdarzenia takie jak: naciśnięcie klawisza na klawiaturze; port szeregowy odbierający znak; i powtarzający się zegar sprzętowy tykający.

Bez tego rodzaju systemu przerwań sprzętowych system operacyjny musiałby być zaśmiecony wywołaniami funkcji, aby regularnie sprawdzać przychodzące naciśnięcia klawiszy, co byłoby marnowaniem mocy procesora, gdy nikt nie pisał, ale nie odpowiadałby wystarczy, kiedy to zrobili.

Jak możesz sobie wyobrazić, wkrótce po PIC pojawił się ulepszony układ o nazwie APIC, zaawansowany rodzaj PIC wbudowanego w sam procesor.

W dzisiejszych czasach interfejsy APIC zapewniają znacznie więcej niż tylko informacje zwrotne z klawiatury, portu szeregowego i zegara systemowego.

Zdarzenia APIC są wyzwalane przez (i dostarczają danych o nich w czasie rzeczywistym) zdarzeniami, takimi jak przegrzanie, i umożliwiają interakcję sprzętową między różnymi rdzeniami we współczesnych procesorach wielordzeniowych.

A dzisiejsze układy Intela, jeśli możemy w dużym uproszczeniu, można ogólnie skonfigurować do pracy na dwa różne sposoby, znane jako Tryb xAPIC i Tryb x2APIC.

Tutaj, xAPIC jest „przestarzałym” sposobem wyodrębniania danych z kontrolera przerwań i x2APIK jest bardziej nowoczesny sposób.

Upraszczając jeszcze bardziej, xAPIC opiera się na tym, co się nazywa MMIO, skrót od wejście/wyjście mapowane w pamięci, do odczytywania danych z interfejsu APIC, gdy rejestruje interesujące zdarzenie.

W trybie MMIO można dowiedzieć się, co wywołało zdarzenie APIC, odczytując dane z określonego obszaru pamięci (RAM), który odzwierciedla rejestry wejścia/wyjścia samego układu APIC.

Te dane xAPIC są mapowane do 4096-bajtowego bloku pamięci gdzieś w fizycznej pamięci RAM komputera.

Upraszcza to dostęp do danych, ale wymaga irytującej, złożonej (i, jak zobaczymy, potencjalnie niebezpiecznej) interakcji między chipem APIC a pamięcią systemową.

W przeciwieństwie do tego x2APIC wymaga: odczytać bezpośrednio dane APIC z samego chipa, używając tak zwanej Rejestry specyficzne dla modelu (MSR).

Według Intela unikanie części MMIO w procesie „zapewnia znacznie zwiększoną adresowalność procesora i pewne ulepszenia w dostarczaniu przerwań”.

Warto zauważyć, że wyodrębnianie danych APIC bezpośrednio z rejestrów na chipie oznacza, że całkowita ilość obsługiwanych danych i maksymalna liczba rdzeni procesora, którymi można zarządzać w tym samym czasie, nie jest ograniczona do 4096 bajtów dostępnych w trybie MMIO.

Jak możesz mieć dane, do których nawet jądro nie może zajrzeć?

Prawdopodobnie już zgadłeś, że dane, które trafiają do obszaru pamięci MMIO, gdy używasz trybu xAPIC, nie zawsze są tak starannie zarządzane, jak powinny…

…a zatem pewien rodzaj „wycieku danych” do tego obszaru MMIO jest sercem tego problemu.

Ale biorąc pod uwagę, że ty już potrzebujesz uprawnień na poziomie administratora aby odczytać dane MMIO w pierwszej kolejności, a zatem prawie na pewno i tak mógłbyś dostać się do wszystkich danych w pamięci…

…dlaczego omyłkowe pojawienie się danych innych osób w obszarze danych APIC MMIO reprezentuje an epicki nieszczelność?

W praktyce może to nieco ułatwić niektóre rodzaje ataków polegających na kradzieży danych lub wyłuskiwaniu pamięci RAM, ale z pewnością nie dałoby ci to więcej możliwości podsłuchiwania pamięci, które już miałeś w teorii?

Niestety, to założenie nie jest prawdziwe, jeśli jakiekolwiek oprogramowanie w systemie korzysta z Intela SGX, skrót od Rozszerzenia ochrony oprogramowania.

DOWIEDZ SIĘ WIĘCEJ O SGX

SGX jest obsługiwany przez wiele najnowszych procesorów Intela i umożliwia jądru systemu operacyjnego „zapieczętowanie” kawałka kodu i danych w fizycznym bloku pamięci RAM, aby utworzyć tak zwaną enklawę.

To sprawia, że zachowuje się, przynajmniej tymczasowo, podobnie jak specjalne chipy bezpieczeństwa w telefonach komórkowych, które są używane do przechowywania sekretów, takich jak klucze deszyfrujące.

Po ustawieniu „blokady” SGX enklawy, tylko kod programu działający w zamkniętym obszarze pamięci może odczytywać i zapisywać zawartość tej pamięci RAM.

W rezultacie wewnętrzne szczegóły wszelkich obliczeń, które mają miejsce po aktywacji enklawy, są niewidoczne dla żadnego innego kodu, wątku, procesu lub użytkownika w systemie.

Łącznie z samym jądrem.

Istnieje sposób na wywołanie kodu, który został zapieczętowany w enklawie, i sposób na zwrócenie wyników obliczeń, które może wykonać, ale nie ma sposobu na odzyskanie, szpiegowanie lub debugowanie kodu i powiązane z nim dane podczas działania.

Enklawa skutecznie zamienia się w czarną skrzynkę, do której można wprowadzać dane wejściowe, takie jak dane, które mają być podpisane kluczem prywatnym, i wyodrębniać dane wyjściowe, takie jak wygenerowany podpis cyfrowy, ale z którego nie można wydobyć kluczy kryptograficznych wykorzystywane w procesie podpisywania.

Jak możesz sobie wyobrazić, jeśli dane, które mają być zapieczętowane wewnątrz enklawy SGX, powinny kiedykolwiek przypadkowo zostać zduplikowane do pamięci RAM MMIO, która jest używana do „odbicia lustrzanego” danych APIC podczas korzystania z trybu „zmapowania pamięci” xAPIC…

…to naruszyłoby bezpieczeństwo SGX, który mówi, że żadne dane nigdy nie powinny wychodzić z enklawy SGX po ich utworzeniu, chyba że są celowo eksportowane przez kod już działający w samej enklawie.

Co powoduje tę epicką porażkę w APIC?

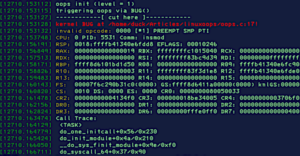

Badacze stojący za ÆPapier przeciekowy PIC odkrył, że organizując odczytywanie danych APIC za pomocą przebiegłej i niezwykłej sekwencji dostępu do pamięci…

…mogą skłonić procesor do zapełnienia przestrzeni APIC MMIO nie tylko danymi świeżo otrzymanymi z samego APIC, ale także danymi, które akurat zostały ostatnio wykorzystane przez procesor w innym celu.

To zachowanie jest efektem ubocznym faktu, że chociaż strona pamięci APIC MMIO ma rozmiar 4096 bajtów, układ APIC w trybie xAPIC w rzeczywistości nie wytwarza danych o wartości 4096 bajtów, a procesor nie zawsze prawidłowo neutralizuje niewykorzystane części regionu MMIO, wypełniając go najpierw zerami.

Zamiast tego stare dane pozostawione w pamięci podręcznej procesora zostały zapisane wraz z nowymi danymi otrzymanymi z samego układu APIC.

Jak to ujęli naukowcy, błąd sprowadza się do tego, co znane jest jako an odczyt niezainicjowanej pamięci, gdzie przypadkowo ponownie wykorzystujesz cudze dane w pamięci RAM, ponieważ ani oni, ani ty nie wyczyściliśmy ich z poprzednich tajemnic.

Czy przeciek ÆPIC ma na mnie wpływ?

Aby zobaczyć pełną listę żetonów, których to dotyczy, zobacz Własne doradztwo firmy Intel.

O ile możemy powiedzieć, jeśli masz procesor Intel 10. lub 11. generacji, prawdopodobnie dotyczy to Ciebie.

Ale jeśli masz zupełnie nowy procesor 12. generacji (najnowszy w momencie pisania), wydaje się, że dotyczy to tylko chipów klasy serwerowej.

Jak na ironię, w laptopach 12. generacji Intel zrezygnował z SGX, więc ten błąd nie dotyczy, ponieważ niemożliwe jest posiadanie jakichkolwiek „zapieczętowanych” enklaw SGX, które mogłyby przeciekać.

Oczywiście, nawet na potencjalnie podatnym chipie, jeśli nie polegasz na żadnym oprogramowaniu, które używa SGX, to błąd też nie dotyczy.

I błąd, dubbing CVE-2022-21233, może zostać wykorzystany tylko przez osobę atakującą, która ma już lokalny dostęp na poziomie administratora (root) do Twojego komputera.

Zwykli użytkownicy nie ma dostępu do bloku danych APIC MMIO, a zatem nie ma możliwości podglądania czegokolwiek tam, nie mówiąc już o tajnych danych, które mogły wyciekać z enklawy SGX.

Tak więc, maszyny wirtualne gości (VM) działające pod kontrolą systemu operacyjnego hosta w hipernadzorcy, takim jak HyperV, VMWare lub VirtualBox, prawie na pewno nie mogą użyć tej sztuczki do wykradania tajemnic od innych gości lub samego hosta.

Dzieje się tak, ponieważ maszyny wirtualne gości zazwyczaj nie uzyskują dostępu do prawdziwych obwodów APIC w procesorze hosta; zamiast tego każdy gość otrzymuje własny symulowany interfejs APIC, który jest unikalny dla tej maszyny wirtualnej.

Co robić?

Nie panikuj.

Na laptopie lub komputerze stacjonarnym możesz nie być w ogóle zagrożony, albo dlatego, że masz starszy (lub, na szczęście, zupełnie nowy!) komputer, albo dlatego, że i tak nie polegasz na SGX.

A nawet jeśli jesteś ryzykowny, każdy, kto dostanie się do twojego laptopa jako administrator/root, prawdopodobnie ma już wystarczającą moc, aby sprawić ci świat kłopotów.

Jeśli masz podatne na ataki serwery i polegasz na SGX jako części swojego bezpieczeństwa operacyjnego, sprawdź Poradnik firmy Intel dotyczący bezpieczeństwa INTEL-SA-00657 informacji o ochronie i łagodzeniu skutków.

Według badaczy, którzy to napisali, „Intel [wypuścił] aktualizacje mikrokodu i SGX Software Development Kit, aby rozwiązać ten problem”.

Zespół jądra Linuksa również wydaje się pracować teraz nad poprawką, która pozwoli Ci skonfigurować system tak, aby zawsze używał x2APIC (który, jak pamiętasz wcześniej, nie przesyła danych APIC przez pamięć współdzieloną), i wdzięcznie zapobiegnie wymuszeniu systemu z powrotem do trybu xAPIC po uruchomieniu.

- APIC

- ÆWyciek PIC

- blockchain

- pomysłowość

- portfele kryptowalutowe

- krypto-wymiana

- kryptografia

- CVE-2022-21233

- bezpieczeństwo cybernetyczne

- cyberprzestępcy

- Bezpieczeństwo cybernetyczne

- Utrata danych

- Departament Bezpieczeństwa Wewnętrznego

- cyfrowe portfele

- EPICKI

- zapora

- Kaspersky

- malware

- Mcafee

- Nagie bezpieczeństwo

- NexBLOC

- plato

- Platon Ai

- Analiza danych Platona

- Gra Platona

- PlatoDane

- platogaming

- SGX

- VPN

- wrażliwość

- zabezpieczenia stron internetowych

- zefirnet

![S3, odc. 111: Ryzyko biznesowe związane z marnym „odfiltrowywaniem nagości” [audio + tekst] S3 Odp111: Ryzyko biznesowe związane z obskurnym „niefiltrem nagości” [Dźwięk + tekst] PlatoBlockchain Data Intelligence. Wyszukiwanie pionowe. AI.](https://platoblockchain.com/wp-content/uploads/2022/08/bn-1200-2-300x157.png)

![S3 Ep93: Bezpieczeństwo biura, koszty naruszenia i spokojne poprawki [Audio + Text] S3 Ep93: Bezpieczeństwo biura, koszty włamań i niespieszne poprawki [Audio + Text] PlatoBlockchain Data Intelligence. Wyszukiwanie pionowe. AI.](https://platoblockchain.com/wp-content/uploads/2022/07/s3-ep93-1200-300x157.png)

![S3, odc.124: Kiedy tak zwane aplikacje zabezpieczające stają się nieuczciwe [audio + tekst] S3, odc.124: Kiedy tak zwane aplikacje zabezpieczające stają się nieuczciwe [audio + tekst]](https://platoblockchain.com/wp-content/uploads/2023/03/s3-ep124-when-so-called-security-apps-go-rogue-audio-text-300x157.png)