Um artigo de pesquisa recém-publicado descreve um chip de computação em memória (CIM) que combina neurônios artificiais com RAM resistiva (RRAM) para que os pesos do modelo de IA possam ser armazenados e processados no mesmo chip.

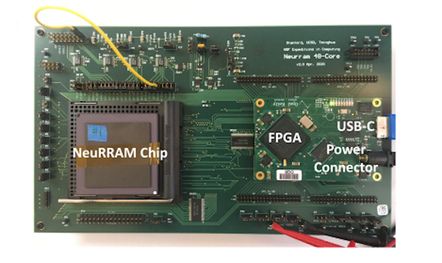

Um chip de computação na memória baseado em memória de acesso aleatório resistiva (clique para ampliar). Imagem: Wan et al

Os pesquisadores por trás do design afirmam que seria mais eficiente para aplicativos de ponta porque elimina a movimentação de dados entre blocos separados de computação e memória.

A computação de ponta e a inteligência artificial estão ambas no caminho certo para um crescimento meteórico num futuro próximo, pelo menos de acordo com a empresa de análise IDC. Alguns cenários os combinam porque as implantações de borda podem ser limitadas em termos de energia e conectividade, mas ainda precisam analisar volumes significativos de dados e fornecer uma resposta quase em tempo real aos eventos, tornando um modelo de IA “vivo” no dispositivo a solução ideal .

Diante disso, um grupo de pesquisadores desenvolveu um chip chamado NeuRRAM, porque combina neurônios artificiais com RRAM em uma arquitetura nova. O objetivo do projeto era fornecer um design que pudesse fornecer simultaneamente alta eficiência energética, bem como versatilidade para suportar vários modelos de IA e precisão comparável à execução do mesmo modelo em software.

O projeto começou inicialmente como parte de um projeto da Nature Science Foundation chamado “Expedições em Computação”. Este projeto reuniu um grupo de pesquisadores de diferentes instituições com diferentes formações, incluindo alguns de Stanford e UCSD, bem como pesquisadores da Universidade Tsinghua, na China, que são especialistas na fabricação de dispositivos RRAM.

Eficiência energética: inferência de IA feita no dispositivo alimentado por bateria

De acordo com Weier Wan, pesquisador graduado da Universidade de Stanford e um dos autores do artigo, publicado ontem na Nature, o NeuRRAM foi desenvolvido como um chip de IA que melhora muito a eficiência energética da inferência de IA, permitindo assim que funções complexas de IA sejam realizadas diretamente em dispositivos de ponta alimentados por bateria, como wearables inteligentes, drones e sensores industriais de IoT. .

“Nos chips de IA atuais, o processamento e o armazenamento de dados acontecem em locais separados – unidade de computação e unidade de memória. A movimentação frequente de dados entre essas unidades consome mais energia e se torna o gargalo para a realização de processadores de IA de baixo consumo de energia para dispositivos de ponta”, disse ele.

Para resolver isso, o chip NeuRRAM implementa um modelo de “computação na memória”, onde o processamento ocorre diretamente na memória. Ele também faz uso de RAM resistiva (RRAM), um tipo de memória que é tão rápido quanto a RAM estática, mas não volátil, permitindo armazenar pesos de modelos de IA. Uma característica importante das células RRAM é que os pesos neurais podem ser armazenados em células de memória como diferentes níveis de condutância, codificados por meio de conversores digital para analógico (DACs) e alimentados na matriz de memória.

Esta não é uma simulação de software, é hardware

Houve estudos anteriores sobre arquiteturas CIM, mas este é o primeiro a demonstrar uma ampla gama de aplicações de IA em hardware e não em simulação de software, ao mesmo tempo que é mais eficiente em termos energéticos e capaz de executar os algoritmos com precisão, algo que nenhum dos estudos anteriores puderam aparecer simultaneamente, segundo Wan.

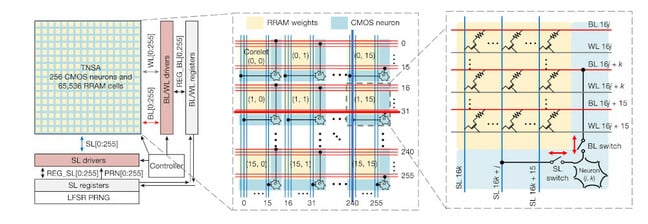

O NeuRRAM consiste em 48 núcleos CIM compreendendo um total de 3 milhões de células RRAM. Cada núcleo é descrito como uma matriz neurossináptica transponível (TNSA) que consiste em uma grade de 256 × 256 células RRAM e 256 circuitos de neurônios artificiais CMOS que implementam conversores analógico-digitais (ADCs) e funções de ativação.

De acordo com o artigo, a arquitetura TNSA foi projetada para oferecer controle flexível da direção dos fluxos de dados, o que é crucial para suportar uma ampla gama de modelos de IA com diferentes padrões de fluxo de dados.

Por exemplo, em redes neurais convolucionais (CNNs) que são comuns em tarefas relacionadas à visão, os dados fluem em uma única direção através de camadas para gerar representações de dados em diferentes níveis de abstração, enquanto em alguns outros modelos a amostragem probabilística é realizada para frente e para trás entre as camadas. até que a rede convirja para um estado de alta probabilidade.

No entanto, outros projetos que combinaram CIM com RRAM foram limitados a operar em uma única direção, normalmente conectando linhas e colunas da matriz de barra transversal RRAM a circuitos dedicados na periferia para acionar entradas e medir saídas, diz o artigo.

Como Funciona

O segredo da reconfigurabilidade do NeuRRAM é que ele distribui os circuitos de neurônios CMOS entre as células RRAM e os conecta ao longo do comprimento de linhas e colunas.

Cada TNSA é dividido em vários corelets, cada um dos quais consiste em 16 × 16 células RRAM e um circuito de neurônios. Os corelets são conectados por linhas de bits (BLs) e linhas de palavras (WLs) compartilhadas ao longo da direção horizontal, e linhas de origem (SLs) ao longo da direção vertical.

O circuito de neurônios se conecta por meio de switches a um BL e um SL dos 16 de cada um que passa pelo corelet, e é responsável por integrar entradas de todas as 256 RRAMs conectadas ao mesmo BL ou SL.

Cada circuito de neurônio pode usar suas chaves BL e SL para entrada e saída. Isso significa que ele pode receber a multiplicação analógica de vetores de matrizes (MVM) de uma célula RRAM proveniente de BL ou SL através dos switches, mas também pode enviar os resultados digitais convertidos para registros periféricos através dos mesmos switches.

Esse arranjo significa que diferentes direções de fluxo de dados podem ser implementadas configurando qual chave usar durante os estágios de entrada e saída de cada circuito de neurônio.

(Essa arquitetura também nos lembra um pouco Chip processador AI do SambaNova, que é implementado como uma grade de unidades de computação e unidades de memória, vinculadas por uma estrutura de comunicação no chip que controla o fluxo de dados.)

Para maximizar o desempenho de inferência de IA usando os 48 núcleos CIM no NeuRRAM, é possível implementar várias estratégias de mapeamento de peso que exploram tanto o paralelismo de modelos quanto o paralelismo de dados, de acordo com o artigo.

No caso de uma CNN, a estratégia pode ser duplicar os pesos das camadas iniciais e de maior intensidade computacional para vários núcleos CIM para inferência paralela. O artigo fornece uma descrição mais detalhada das estratégias de mapeamento de peso disponíveis.

O artigo relata resultados de inferência medidos por hardware usando o chip para uma série de tarefas de IA, incluindo classificações de imagens usando conjuntos de dados CIFAR-10 e MNIST, reconhecimento de comando de fala do Google e recuperação de imagem MNIST, implementados com vários modelos de IA.

Alega-se que alcança precisão de inferência comparável a modelos de software treinados com pesos de 4 bits em todas essas tarefas de benchmark. Por exemplo, ele atinge uma taxa de erro de 0.98% no reconhecimento de dígitos manuscritos MNIST usando uma CNN de 7 camadas, uma taxa de erro de 14.34% na classificação de objetos CIFAR-10 usando ResNet-20 e uma taxa de erro de 15.34% no reconhecimento de comando de fala do Google usando um LSTM de 4 células (memória de longo prazo).

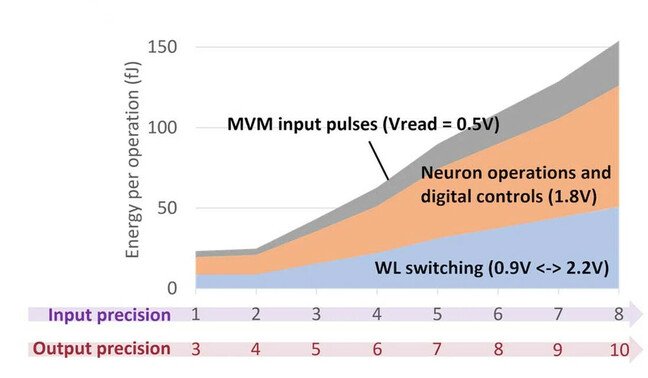

O chip NeuRRAM também possui uma eficiência energética duas vezes melhor do que os designs anteriores de chips CIM usando RRAM, em várias precisões de bits computacionais. No entanto, o consumo de energia no artigo não é citado de uma forma que seja fácil de comparar com dispositivos comerciais no mercado, e a figura abaixo ilustra o consumo de energia por operação em diferentes precisões de bits medidas em femtojoules (fJ).

No entanto, Wan nos disse que, para uma tarefa típica de localização de palavras-chave em tempo real que é executada em muitos dispositivos domésticos inteligentes hoje (como dizer a um alto-falante inteligente para acender a luz), estima-se que NeuRRAM consuma menos de 2 microwatts de energia.

“Isso significa que mesmo com uma pequena bateria tipo moeda, ela pode funcionar por mais de 10 anos (sem considerar a energia consumida por outros componentes do sistema)”, disse ele.

Segundo o artigo, o chip é fabricado com tecnologia CMOS de 130 nm, e espera-se que a eficiência energética melhore com o dimensionamento da tecnologia, como é o caso de outros produtos semicondutores.

A produção ainda está a anos de distância

Então, veremos um dispositivo comercial baseado nesta tecnologia? Wan diz que tem grande potencial para ser comercializado e está pensando pessoalmente em trabalhar para produzi-lo sozinho.

“O caso de uso inicial mais adequado é muito provavelmente em edge extrema/IoT”, ele nos disse.

Um produto baseado no chip NeuRRAM pode ser combinado em um sistema com CPU, como acontece com outros aceleradores, mas isso não é necessário para todas as aplicações.

“Recentemente, tem havido uma tendência de os dados dos sensores serem alimentados diretamente aos processadores de IA sem passar pela CPU ou memória extra”, disse Wan, mas acrescentou que, para a maioria dos casos de implantação no mundo real, esses aceleradores de IA funcionam como um coprocessador. para uma CPU, onde a CPU gerencia outras tarefas.

O chip NeuRRAM destina-se apenas ao trabalho de inferência, em grande parte porque a tecnologia RRAM em sua forma atual não é muito adequada para treinamento porque o processo de treinamento requer atualizações frequentes da memória, e esta é “uma operação muito cara em RRAM”, disse Wan.

“Atualmente, muitas fundições comerciais já têm a capacidade de fabricar dispositivos RRAM, mas principalmente para uso de memória incorporada, e não para computação na memória. Assim que o processo RRAM se tornar mais amplamente disponível para os projetistas de IC, um produto NeuRRAM poderá acontecer.”

No entanto, é difícil prever o cronograma exato para que isso aconteça, e Wan disse que pode ser nos próximos dois a três anos, ou muito mais. ®

- AI

- arte ai

- gerador de arte ai

- ai robô

- inteligência artificial

- certificação de inteligência artificial

- inteligência artificial em bancos

- robô de inteligência artificial

- robôs de inteligência artificial

- software de inteligência artificial

- blockchain

- conferência blockchain ai

- Coingenius

- inteligência artificial conversacional

- conferência de criptografia ai

- dall's

- deep learning

- google ai

- aprendizado de máquina

- platão

- platão ai

- Inteligência de Dados Platão

- Jogo de Platão

- PlatãoData

- jogo de platô

- escala ai

- sintaxe

- O registro

- zefirnet