บทความวิจัยที่ตีพิมพ์ใหม่อธิบายถึงชิปประมวลผลในหน่วยความจำ (CIM) ที่รวมเซลล์ประสาทเทียมกับ RAM ตัวต้านทาน (RRAM) เพื่อให้สามารถจัดเก็บและประมวลผลน้ำหนักของแบบจำลอง AI บนชิปตัวเดียวกันได้

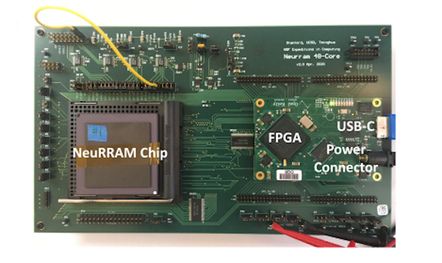

ชิปประมวลผลในหน่วยความจำที่ใช้หน่วยความจำเข้าถึงโดยสุ่มแบบต้านทาน (คลิกเพื่อดูภาพขยาย) รูปภาพ: Wan et al

นักวิจัยที่อยู่เบื้องหลังการออกแบบอ้างว่าจะมีประสิทธิภาพมากขึ้นสำหรับแอพพลิเคชั่นขอบเพราะช่วยขจัดการเคลื่อนย้ายข้อมูลระหว่างการคำนวณแยกจากกันและบล็อกหน่วยความจำ

Edge Computing และปัญญาประดิษฐ์กำลังติดตามการเติบโตของอุตุนิยมวิทยาในอนาคตอันใกล้นี้อย่างน้อย ตามที่บริษัทวิเคราะห์ IDC. บางสถานการณ์รวมเข้าด้วยกันเนื่องจากการปรับใช้ Edge อาจมีข้อจำกัดในด้านพลังงานและการเชื่อมต่อ แต่ยังคงต้องวิเคราะห์ข้อมูลจำนวนมากและส่งมอบการตอบสนองที่ใกล้เคียงกับเรียลไทม์ต่อเหตุการณ์ ทำให้โมเดล AI "มีชีวิต" ในอุปกรณ์เป็นโซลูชันที่เหมาะสมที่สุด .

ด้วยเหตุนี้ กลุ่มนักวิจัยจึงได้พัฒนาชิปที่เรียกว่า NeuRRAM เนื่องจากเป็นการรวมเซลล์ประสาทเทียมกับ RRAM ในสถาปัตยกรรมใหม่ เป้าหมายของโครงการคือการนำเสนอการออกแบบที่สามารถให้ประสิทธิภาพการใช้พลังงานสูงพร้อมๆ กัน รวมถึงความเก่งกาจเพื่อรองรับโมเดล AI ต่างๆ และความแม่นยำที่เทียบเท่ากับการเรียกใช้ซอฟต์แวร์รุ่นเดียวกันในซอฟต์แวร์

โครงการนี้เริ่มต้นขึ้นโดยเป็นส่วนหนึ่งของโครงการ Nature Science Foundation ที่เรียกว่า "Expeditions in Computing" โครงการนี้รวบรวมกลุ่มนักวิจัยจากสถาบันต่างๆ ที่มีภูมิหลังต่างกัน รวมถึงบางส่วนจาก Stanford และ UCSD รวมถึงนักวิจัยจากมหาวิทยาลัย Tsinghua ในประเทศจีนซึ่งเป็นผู้เชี่ยวชาญในการผลิตอุปกรณ์ RRAM

ประสิทธิภาพการใช้พลังงาน: การอนุมาน AI กับ gizmo ที่ใช้พลังงานจากแบตเตอรี่

ตามที่ Weier Wan นักวิจัยระดับบัณฑิตศึกษาที่มหาวิทยาลัยสแตนฟอร์ดและหนึ่งใน ผู้เขียนบทความNeuRRAM ซึ่งเผยแพร่ใน Nature เมื่อวานนี้ ได้รับการพัฒนาให้เป็นชิป AI ที่ปรับปรุงประสิทธิภาพการใช้พลังงานอย่างมากของการอนุมาน AI ซึ่งช่วยให้รับรู้ฟังก์ชัน AI ที่ซับซ้อนได้โดยตรงภายในอุปกรณ์ Edge ที่ใช้พลังงานจากแบตเตอรี่ เช่น อุปกรณ์สวมใส่อัจฉริยะ โดรน และเซ็นเซอร์ IoT ในอุตสาหกรรม .

“ในชิป AI ในปัจจุบัน การประมวลผลข้อมูลและการจัดเก็บข้อมูลเกิดขึ้นในที่ที่แยกจากกัน – หน่วยประมวลผลและหน่วยหน่วยความจำ การย้ายข้อมูลบ่อยครั้งระหว่างหน่วยเหล่านี้ใช้พลังงานมากที่สุดและกลายเป็นคอขวดสำหรับการตระหนักถึงโปรเซสเซอร์ AI ที่ใช้พลังงานต่ำสำหรับอุปกรณ์ Edge” เขากล่าว

เพื่อแก้ไขปัญหานี้ ชิป NeuRRAM ใช้โมเดล "คำนวณในหน่วยความจำ" ซึ่งการประมวลผลจะเกิดขึ้นโดยตรงภายในหน่วยความจำ นอกจากนี้ยังใช้ RAM แบบต้านทาน (RRAM) ซึ่งเป็นหน่วยความจำประเภทที่เร็วเท่ากับ RAM แบบคงที่แต่ไม่ลบเลือน ทำให้สามารถจัดเก็บน้ำหนักแบบจำลอง AI ได้ คุณลักษณะสำคัญของเซลล์ RRAM คือน้ำหนักของระบบประสาทสามารถเก็บไว้ในเซลล์หน่วยความจำตามระดับการนำไฟฟ้าที่แตกต่างกัน โดยเข้ารหัสผ่านตัวแปลงดิจิทัลเป็นแอนะล็อก (DAC) และป้อนไปยังอาร์เรย์หน่วยความจำ

นี่ไม่ใช่การจำลองซอฟต์แวร์ แต่เป็นฮาร์ดแวร์

มีการศึกษาก่อนหน้านี้เกี่ยวกับสถาปัตยกรรม CIM แต่นี่เป็นครั้งแรกที่แสดงให้เห็นถึงการใช้งาน AI ที่หลากหลายในฮาร์ดแวร์มากกว่าในการจำลองซอฟต์แวร์ ในขณะที่ประหยัดพลังงานมากกว่าและสามารถเรียกใช้อัลกอริทึมได้อย่างแม่นยำ ซึ่งไม่มีการศึกษาก่อนหน้านี้ สามารถแสดงพร้อมกันได้ตามต้องการ

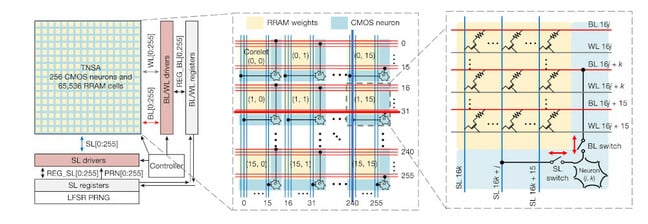

NeuRRAM ประกอบด้วยแกน CIM 48 คอร์ที่ประกอบด้วยเซลล์ RRAM ทั้งหมด 3 ล้านเซลล์ แต่ละคอร์ถูกอธิบายว่าเป็นอาร์เรย์ neurosynaptic แบบทรานส์โพซิชั่น (TNSA) ซึ่งประกอบด้วยตารางเซลล์ RRAM 256 × 256 และวงจรเซลล์ประสาทเทียม CMOS 256 ตัวที่ใช้ตัวแปลงแอนะล็อกเป็นดิจิทัล (ADC) และฟังก์ชันการเปิดใช้งาน

จากรายงานดังกล่าว สถาปัตยกรรม TNSA ได้รับการออกแบบมาเพื่อให้สามารถควบคุมทิศทางของกระแสข้อมูลได้อย่างยืดหยุ่น ซึ่งเป็นสิ่งสำคัญสำหรับการสนับสนุนโมเดล AI ที่หลากหลายด้วยรูปแบบการไหลของข้อมูลที่แตกต่างกัน

ตัวอย่างเช่น ใน Convolutional Neural Network (CNNs) ที่พบได้ทั่วไปในงานที่เกี่ยวข้องกับการมองเห็น ข้อมูลจะไหลไปในทิศทางเดียวผ่านเลเยอร์เพื่อสร้างการแสดงข้อมูลในระดับนามธรรมที่แตกต่างกัน ในขณะที่แบบจำลองอื่นๆ บางตัวจะสุ่มตัวอย่างความน่าจะเป็นไปมาระหว่างเลเยอร์ จนกระทั่งเครือข่ายมาบรรจบกันเป็นสถานะที่มีความน่าจะเป็นสูง

อย่างไรก็ตาม การออกแบบอื่น ๆ ที่รวม CIM กับ RRAM นั้นถูกจำกัดให้ทำงานในทิศทางเดียว โดยทั่วไปโดยการเดินสายแถวและคอลัมน์ของอาร์เรย์ครอสบาร์ RRAM ไปยังวงจรเฉพาะบนขอบด้านนอกเพื่อขับเคลื่อนอินพุตและวัดเอาต์พุต

วิธีการทำงาน

เคล็ดลับในการกำหนดค่าใหม่ของ NeuRRAM คือการกระจายวงจรเซลล์ประสาท CMOS ระหว่างเซลล์ RRAM และเชื่อมต่อไปตามความยาวของทั้งแถวและคอลัมน์

แต่ละ TNSA ถูกแบ่งออกเป็นคอร์เล็ตจำนวนหนึ่ง ซึ่งแต่ละอันประกอบด้วยเซลล์ RRAM ขนาด 16 × 16 และวงจรเซลล์ประสาทหนึ่งวงจร corelets เชื่อมต่อกันด้วย bit-lines (BLs) และ word-lines (WLs) ที่ใช้ร่วมกันตามแนวนอน และ source-lines (SLs) ตามทิศทางแนวตั้ง

วงจรเซลล์ประสาทเชื่อมต่อผ่านสวิตช์ไปยัง BL หนึ่งตัวและ SL หนึ่งตัวจากทั้งหมด 16 ตัวที่ผ่านแกนกลาง และมีหน้าที่ในการรวมอินพุตจาก 256 RRAM ทั้งหมดที่เชื่อมต่อกับ BL หรือ SL เดียวกัน

วงจรเซลล์ประสาทแต่ละวงจรสามารถใช้สวิตช์ BL และ SL สำหรับอินพุตและเอาต์พุต ซึ่งหมายความว่าสามารถรับการคูณเมทริกซ์เวกเตอร์แบบอะนาล็อก (MVM) จากเซลล์ RRAM ที่มาจาก BL หรือ SL ผ่านสวิตช์ แต่ยังสามารถส่งผลดิจิทัลที่แปลงแล้วไปยังรีจิสเตอร์ต่อพ่วงผ่านสวิตช์เดียวกัน

การจัดเรียงนี้หมายความว่าทิศทางการไหลของข้อมูลที่แตกต่างกันสามารถทำได้โดยการกำหนดค่าสวิตช์ที่จะใช้ระหว่างขั้นตอนอินพุตและเอาต์พุตของวงจรเซลล์ประสาทแต่ละวงจร

(สถาปัตยกรรมนี้ยังทำให้เรานึกถึง ชิปประมวลผล AI ของ SambaNovaซึ่งใช้งานเป็นกริดของหน่วยประมวลผลและหน่วยหน่วยความจำ เชื่อมโยงกันด้วยแฟบริกการสื่อสารบนชิปที่ควบคุมกระแสข้อมูล)

ในการเพิ่มประสิทธิภาพการอนุมาน AI ให้สูงสุดโดยใช้แกน CIM 48 คอร์ใน NeuRRAM มีความเป็นไปได้ที่จะใช้กลยุทธ์การทำแผนที่น้ำหนักแบบต่างๆ ที่ใช้ประโยชน์จากทั้งแบบจำลองแบบขนานและแบบคู่ขนานของข้อมูล

ในกรณีของ CNN กลยุทธ์อาจเป็นการทำซ้ำน้ำหนักของเลเยอร์ต้นๆ ที่เน้นการประมวลผลมากที่สุดไปยังคอร์ CIM หลายคอร์สำหรับการอนุมานแบบคู่ขนาน บทความนี้ให้คำอธิบายโดยละเอียดเพิ่มเติมเกี่ยวกับกลยุทธ์การทำแผนที่น้ำหนักที่มีอยู่

รายงานรายงานผลการอนุมานที่วัดด้วยฮาร์ดแวร์โดยใช้ชิปสำหรับงาน AI ต่างๆ รวมถึงการจำแนกรูปภาพโดยใช้ชุดข้อมูล CIFAR-10 และ MNIST การรู้จำคำสั่งเสียงของ Google และการกู้คืนรูปภาพ MNIST ใช้กับโมเดล AI ต่างๆ

มีการอ้างว่าบรรลุความแม่นยำในการอนุมานเทียบได้กับรุ่นซอฟต์แวร์ที่ได้รับการฝึกฝนด้วยตุ้มน้ำหนัก 4 บิตในงานวัดประสิทธิภาพเหล่านี้ทั้งหมด ตัวอย่างเช่น มีอัตราข้อผิดพลาด 0.98 เปอร์เซ็นต์ในการจดจำตัวเลขที่เขียนด้วยลายมือของ MNIST โดยใช้ CNN 7 เลเยอร์ อัตราข้อผิดพลาด 14.34 เปอร์เซ็นต์ในการจำแนกประเภทวัตถุ CIFAR-10 โดยใช้ ResNet-20 และอัตราข้อผิดพลาด 15.34 เปอร์เซ็นต์ในการรู้จำคำสั่งเสียงของ Google โดยใช้ LSTM 4 เซลล์ (หน่วยความจำระยะสั้นระยะยาว)

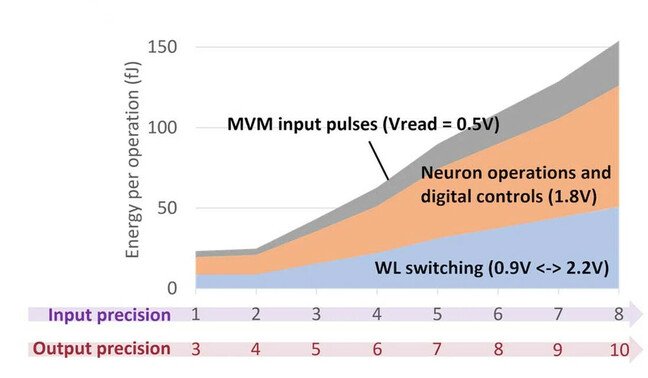

ชิป NeuRRAM ยังอ้างว่ามีประสิทธิภาพในการใช้พลังงานที่ดีกว่าการออกแบบชิป CIM รุ่นก่อนถึงสองเท่าโดยใช้ RRAM ผ่านความแม่นยำบิตการคำนวณต่างๆ อย่างไรก็ตาม การใช้พลังงานในกระดาษไม่ได้ระบุไว้ในรูปแบบที่ง่ายต่อการเปรียบเทียบกับอุปกรณ์เชิงพาณิชย์ในตลาด และรูปที่แสดงด้านล่างแสดงให้เห็นถึงการใช้พลังงานต่อการทำงานในบิตที่มีความแม่นยำต่างกันซึ่งวัดเป็น femtojoules (fJ)

อย่างไรก็ตาม Wan บอกเราว่าสำหรับงานระบุคำหลักแบบเรียลไทม์ทั่วไปที่ทำงานบนอุปกรณ์สมาร์ทโฮมจำนวนมากในปัจจุบัน (เช่น การบอกให้ลำโพงอัจฉริยะเปิดไฟ) NeuRRAM คาดว่าจะใช้พลังงานน้อยกว่า 2 ไมโครวัตต์

“นั่นหมายถึงแม้ในแบตเตอรี่แบบเหรียญขนาดเล็ก มันสามารถทำงานได้นานกว่า 10 ปี (ไม่คำนึงถึงพลังงานที่ใช้โดยส่วนประกอบอื่นๆ ของระบบ)” เขากล่าว

อ้างอิงจากรายงาน ชิปถูกประดิษฐ์ขึ้นโดยใช้เทคโนโลยี 130nm CMOS และคาดว่าประสิทธิภาพการใช้พลังงานจะดีขึ้นด้วยการปรับขนาดเทคโนโลยี เช่นเดียวกับผลิตภัณฑ์เซมิคอนดักเตอร์อื่นๆ

การผลิตยังคงอยู่ห่างออกไปหลายปี

แล้วเราจะเห็นอุปกรณ์การขนส่งเชิงพาณิชย์ที่ใช้เทคโนโลยีนี้หรือไม่? Wan กล่าวว่ามีศักยภาพที่ดีที่จะนำไปขายในเชิงพาณิชย์ และโดยส่วนตัวแล้วกำลังพิจารณาที่จะผลิตมันขึ้นมาเอง

“กรณีการใช้งานเริ่มต้นที่เหมาะสมที่สุดมีแนวโน้มสูงใน edge / IoT ที่รุนแรง” เขาบอกกับเรา

ผลิตภัณฑ์ที่ใช้ชิป NeuRRAM สามารถรวมเข้ากับระบบที่มี CPU ได้ เช่นเดียวกับตัวเร่งความเร็วอื่นๆ แต่สิ่งนี้ไม่จำเป็นสำหรับทุกแอปพลิเคชัน

“เมื่อเร็ว ๆ นี้มีแนวโน้มของข้อมูลจากเซ็นเซอร์ที่ป้อนโดยตรงไปยังโปรเซสเซอร์ AI โดยไม่ต้องผ่าน CPU หรือหน่วยความจำเพิ่มเติม” Wan กล่าว แต่เขาเสริมว่าสำหรับกรณีการใช้งานจริงส่วนใหญ่ ตัวเร่ง AI ดังกล่าวทำหน้าที่เป็นตัวประมวลผลร่วม สำหรับ CPU โดยที่ CPU จะจัดการงานอื่นๆ

ชิป NeuRRAM มีไว้สำหรับงานอนุมานเท่านั้น ส่วนใหญ่เป็นเพราะเทคโนโลยี RRAM ในรูปแบบปัจจุบันไม่เหมาะสำหรับการฝึกอบรมมากนัก เนื่องจากกระบวนการฝึกอบรมต้องการการอัปเดตหน่วยความจำบ่อยครั้ง และนี่เป็น "การดำเนินการ RRAM ที่มีราคาแพงมาก" Wan กล่าว

“ปัจจุบัน โรงหล่อเชิงพาณิชย์จำนวนมากมีความสามารถในการผลิตอุปกรณ์ RRAM ได้แล้ว แต่ส่วนใหญ่สำหรับหน่วยความจำแบบฝังจะใช้มากกว่าสำหรับการประมวลผลในหน่วยความจำ เมื่อกระบวนการ RRAM กลายเป็นที่แพร่หลายมากขึ้นสำหรับนักออกแบบ IC ผลิตภัณฑ์ NeuRRAM ก็อาจเกิดขึ้นได้”

ไทม์ไลน์ที่แน่นอนสำหรับสิ่งนี้เกิดขึ้นได้ยาก อย่างไรก็ตาม Wan กล่าวว่าอาจอยู่ในสองถึงสามปีข้างหน้าหรือนานกว่านั้นมาก ®

- AI

- ไอ อาร์ต

- เครื่องกำเนิดไออาร์ท

- หุ่นยนต์ไอ

- ปัญญาประดิษฐ์

- ใบรับรองปัญญาประดิษฐ์

- ปัญญาประดิษฐ์ในการธนาคาร

- หุ่นยนต์ปัญญาประดิษฐ์

- หุ่นยนต์ปัญญาประดิษฐ์

- ซอฟต์แวร์ปัญญาประดิษฐ์

- blockchain

- การประชุม blockchain ai

- เหรียญอัจฉริยะ

- ปัญญาประดิษฐ์สนทนา

- การประชุม crypto ai

- ดัล-อี

- การเรียนรู้ลึก ๆ

- google ai

- เรียนรู้เครื่อง

- เพลโต

- เพลโตไอ

- เพลโตดาต้าอินเทลลิเจนซ์

- เกมเพลโต

- เพลโตดาต้า

- เพลโตเกม

- ขนาดไอ

- วากยสัมพันธ์

- ลงทะเบียน

- ลมทะเล