Một bài báo nghiên cứu mới được xuất bản mô tả một chip máy tính trong bộ nhớ (CIM) kết hợp các tế bào thần kinh nhân tạo với RAM điện trở (RRAM) để các trọng số mô hình AI có thể được lưu trữ và xử lý trên cùng một con chip.

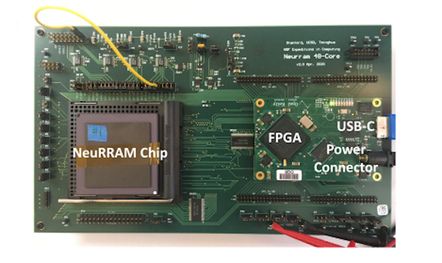

Một chip điện toán trong bộ nhớ dựa trên bộ nhớ truy cập ngẫu nhiên điện trở (bấm để phóng to). Hình ảnh: Wan et al

Các nhà nghiên cứu đằng sau thiết kế tuyên bố rằng nó sẽ hiệu quả hơn cho các ứng dụng biên vì nó loại bỏ sự di chuyển dữ liệu giữa các khối máy tính và bộ nhớ riêng biệt.

Điện toán biên và trí tuệ nhân tạo đều đang trên đà phát triển theo hướng địa lý trong tương lai gần, ít nhất là theo công ty phân tích IDC. Một số kịch bản kết hợp chúng lại với nhau vì việc triển khai ở biên có thể bị hạn chế về nguồn điện và khả năng kết nối, nhưng vẫn cần phân tích khối lượng dữ liệu đáng kể và đưa ra phản hồi gần như theo thời gian thực cho các sự kiện, khiến mô hình AI “sống” trong thiết bị trở thành giải pháp tối ưu nhất .

Về vấn đề này, một nhóm các nhà nghiên cứu đã phát triển một con chip mà nó gọi là NeuRRAM, bởi vì nó kết hợp các tế bào thần kinh nhân tạo với RRAM trong một kiến trúc mới. Mục tiêu của dự án là cung cấp một thiết kế có thể đồng thời mang lại hiệu quả năng lượng cao cũng như tính linh hoạt để hỗ trợ các mô hình AI khác nhau và độ chính xác tương đương với việc chạy cùng một mô hình trong phần mềm.

Dự án ban đầu bắt đầu như một phần của dự án của Quỹ Khoa học Tự nhiên có tên là “Cuộc thám hiểm trong Máy tính”. Dự án này tập hợp một nhóm các nhà nghiên cứu từ các tổ chức khác nhau có nền tảng khác nhau, bao gồm một số từ Stanford và UCSD, cũng như các nhà nghiên cứu tại Đại học Thanh Hoa ở Trung Quốc là những chuyên gia về chế tạo thiết bị RRAM.

Hiệu quả năng lượng: Suy luận của AI được thực hiện trên gizmo chạy bằng pin

Theo Weier Wan, một nhà nghiên cứu sau đại học tại Đại học Stanford và là một trong những tác giả của bài báo, được công bố trên tạp chí Nature ngày hôm qua, NeuRRAM đã được phát triển như một chip AI giúp cải thiện đáng kể hiệu quả năng lượng của suy luận AI, do đó cho phép các chức năng AI phức tạp được thực hiện trực tiếp trong các thiết bị cạnh chạy bằng pin, chẳng hạn như thiết bị đeo thông minh, máy bay không người lái và cảm biến IoT công nghiệp .

“Trong các chip AI ngày nay, việc xử lý và lưu trữ dữ liệu diễn ra ở những nơi riêng biệt – đơn vị tính toán và đơn vị bộ nhớ. Ông nói: “Việc di chuyển dữ liệu thường xuyên giữa các đơn vị này tiêu tốn nhiều năng lượng nhất và trở thành nút thắt cổ chai trong việc hiện thực hóa bộ xử lý AI tiêu thụ điện năng thấp cho các thiết bị biên”.

Để giải quyết vấn đề này, chip NeuRRAM triển khai mô hình “tính toán trong bộ nhớ”, trong đó quá trình xử lý diễn ra trực tiếp trong bộ nhớ. Nó cũng sử dụng RAM điện trở (RRAM), một loại bộ nhớ có tốc độ nhanh như RAM tĩnh nhưng không dễ bay hơi, cho phép nó lưu trữ trọng lượng mô hình AI. Một tính năng chính của tế bào RRAM là trọng lượng thần kinh có thể được lưu trữ trong các tế bào bộ nhớ ở các mức độ dẫn khác nhau, được mã hóa thông qua bộ chuyển đổi kỹ thuật số sang tương tự (DAC) và được đưa vào mảng bộ nhớ.

Đây không phải là mô phỏng phần mềm, đây là phần cứng

Đã có những nghiên cứu trước đây về kiến trúc CIM, nhưng đây là nghiên cứu đầu tiên chứng minh một loạt các ứng dụng AI trong phần cứng hơn là trong mô phỏng phần mềm, đồng thời tiết kiệm năng lượng hơn và có thể chạy các thuật toán chính xác, điều mà chưa có nghiên cứu nào trước đây đã có thể hiển thị đồng thời, theo Wan.

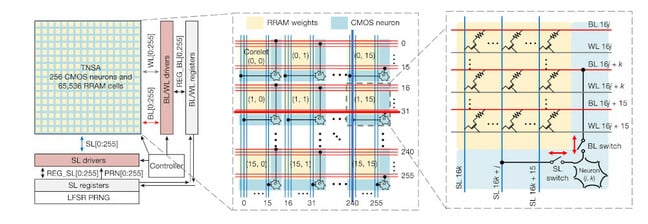

NeuRRAM bao gồm 48 lõi CIM bao gồm tổng số 3 triệu tế bào RRAM. Mỗi lõi được mô tả như một mảng tiếp hợp thần kinh có thể chuyển đổi (TNSA) bao gồm một mạng lưới 256 × 256 tế bào RRAM và 256 mạch nơ-ron nhân tạo CMOS thực hiện các bộ chuyển đổi tương tự-kỹ thuật số (ADC) và các chức năng kích hoạt.

Theo bài báo, kiến trúc TNSA đã được thiết kế để cung cấp khả năng kiểm soát linh hoạt hướng của các luồng dữ liệu, điều này rất quan trọng để hỗ trợ một loạt các mô hình AI với các mẫu luồng dữ liệu khác nhau.

Ví dụ: trong mạng nơ-ron tích tụ (CNN) phổ biến trong các nhiệm vụ liên quan đến thị giác, dữ liệu chảy theo một hướng duy nhất qua các lớp để tạo ra các biểu diễn dữ liệu ở các mức trừu tượng khác nhau, trong khi ở một số mô hình khác, lấy mẫu theo xác suất được thực hiện qua lại giữa các lớp cho đến khi mạng hội tụ về trạng thái xác suất cao.

Tuy nhiên, các thiết kế khác kết hợp CIM với RRAM bị giới hạn ở việc hoạt động theo một hướng, thường là bằng cách nối các hàng và cột của dãy thanh ngang RRAM tới các mạch chuyên dụng ở ngoại vi để điều khiển đầu vào và đo lường đầu ra, bài báo cho biết.

Cách thức thực hiện

Bí mật về khả năng cấu hình lại của NeuRRAM là nó phân phối các mạch nơ-ron CMOS giữa các ô RRAM và kết nối chúng dọc theo chiều dài của cả hàng và cột.

Mỗi TNSA được chia thành một số lõi con, mỗi lõi bao gồm 16 × 16 tế bào RRAM và một mạch nơ-ron. Các lõi con được kết nối bằng các đường bit chia sẻ (BL) và các dòng từ (WL) dọc theo hướng ngang, và các đường nguồn (SL) theo hướng dọc.

Mạch nơ-ron kết nối qua bộ chuyển mạch tới một BL và một SL trong số 16 bộ chuyển mạch đi qua corelet, và chịu trách nhiệm tích hợp đầu vào từ tất cả 256 RRAM kết nối với cùng một BL hoặc SL.

Mỗi mạch nơron có thể sử dụng các công tắc BL và SL của nó cho đầu vào và đầu ra. Điều này có nghĩa là nó có thể nhận phép nhân vectơ ma trận tương tự (MVM) từ một ô RRAM đến từ BL hoặc SL thông qua các bộ chuyển mạch, nhưng cũng có thể gửi kết quả kỹ thuật số đã chuyển đổi đến các thanh ghi ngoại vi thông qua các bộ chuyển mạch tương tự.

Sự sắp xếp này có nghĩa là các hướng luồng dữ liệu khác nhau có thể được thực hiện bằng cách định cấu hình công tắc nào sẽ sử dụng trong các giai đoạn đầu vào và đầu ra của mỗi mạch nơ-ron.

(Kiến trúc này cũng khiến chúng ta nhớ đến phần nào Chip xử lý AI của SambaNova, được triển khai dưới dạng lưới các đơn vị máy tính và đơn vị bộ nhớ, được liên kết bởi một kết cấu giao tiếp trên chip điều khiển luồng dữ liệu.)

Theo bài báo, để tối đa hóa hiệu suất suy luận của AI bằng cách sử dụng 48 lõi CIM trong NeuRRAM, có thể thực hiện các chiến lược lập bản đồ trọng số khác nhau khai thác cả song song mô hình và song song dữ liệu.

Trong trường hợp của CNN, chiến lược có thể là sao chép trọng số của các lớp đầu tiên, chuyên sâu về tính toán nhất thành nhiều lõi CIM để truyền thông song song. Bài báo cung cấp mô tả chi tiết hơn về các chiến lược lập bản đồ trọng lượng có sẵn.

Bài báo báo cáo kết quả suy luận được đo bằng phần cứng bằng cách sử dụng chip cho một loạt các tác vụ AI bao gồm phân loại hình ảnh bằng cách sử dụng bộ dữ liệu CIFAR-10 và MNIST, nhận dạng lệnh giọng nói của Google và khôi phục hình ảnh MNIST, được thực hiện với các mô hình AI khác nhau.

Nó được tuyên bố là đạt được độ chính xác suy luận tương đương với các mô hình phần mềm được đào tạo với trọng số 4 bit trên tất cả các tác vụ điểm chuẩn này. Ví dụ: nó đạt được tỷ lệ lỗi 0.98 phần trăm khi nhận dạng chữ số viết tay MNIST bằng CNN 7 lớp, tỷ lệ lỗi 14.34 phần trăm khi phân loại đối tượng CIFAR-10 sử dụng ResNet-20 và tỷ lệ lỗi 15.34 phần trăm khi nhận dạng lệnh giọng nói của Google bằng cách sử dụng LSTM 4 ô (bộ nhớ ngắn hạn dài).

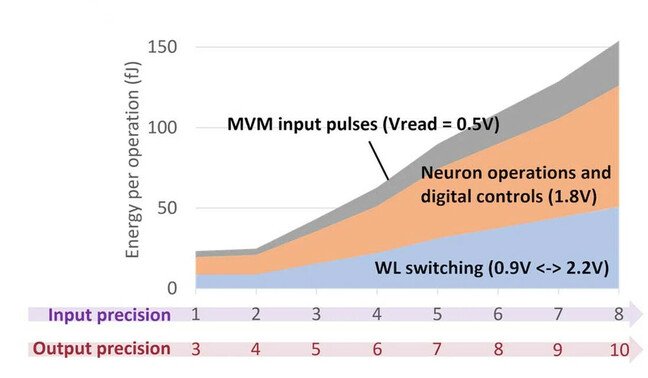

Chip NeuRRAM cũng được cho là có hiệu suất năng lượng tốt hơn gấp hai lần so với các thiết kế chip CIM trước đó sử dụng RRAM, trên nhiều độ chính xác bit tính toán khác nhau. Tuy nhiên, mức tiêu thụ năng lượng trong bài báo không được trích dẫn ở dạng dễ dàng so sánh với các thiết bị thương mại trên thị trường và hình dưới đây minh họa mức tiêu thụ năng lượng cho mỗi hoạt động ở các độ chính xác bit khác nhau được đo bằng femtojoules (fJ).

Tuy nhiên, Wan nói với chúng tôi rằng đối với tác vụ phát hiện từ khóa thời gian thực điển hình chạy trên nhiều thiết bị gia đình thông minh hiện nay (chẳng hạn như yêu cầu loa thông minh bật đèn), NeuRRAM được ước tính tiêu thụ ít hơn 2 microwatts điện năng.

Ông nói: “Điều đó có nghĩa là ngay cả trên một cục pin nhỏ bằng đồng xu, nó có thể chạy hơn 10 năm (không tính đến năng lượng tiêu thụ của các thành phần hệ thống khác).

Theo bài báo, con chip này được chế tạo bằng công nghệ CMOS 130nm và dự kiến sẽ cải thiện hiệu suất năng lượng khi mở rộng quy mô công nghệ, giống như trường hợp của các sản phẩm bán dẫn khác.

Quá trình sản xuất vẫn còn nhiều năm nữa

Vì vậy, chúng ta sẽ thấy một thiết bị thương mại vận chuyển dựa trên công nghệ này? Wan nói rằng nó có tiềm năng lớn để được thương mại hóa và cá nhân đang xem xét việc tự sản xuất nó.

Ông nói với chúng tôi: “Trường hợp sử dụng ban đầu phù hợp nhất rất có thể xảy ra là ở cực kỳ cạnh / IoT.

Một sản phẩm dựa trên chip NeuRRAM có thể được kết hợp trong một hệ thống với CPU, như với các bộ tăng tốc khác, nhưng điều này không cần thiết cho mọi ứng dụng.

Wan cho biết: “Gần đây đã có xu hướng dữ liệu từ các cảm biến được đưa trực tiếp đến bộ xử lý AI mà không cần thông qua CPU hoặc bộ nhớ phụ cho một CPU, nơi CPU quản lý các tác vụ khác.

Chip NeuRRAM chỉ dành cho công việc truyền thông tin, phần lớn là do công nghệ RRAM ở dạng hiện tại không phù hợp lắm cho việc đào tạo vì quá trình đào tạo đòi hỏi phải cập nhật bộ nhớ thường xuyên và đây là “một hoạt động rất tốn kém trên RRAM” Wan nói.

“Hiện tại nhiều xưởng đúc thương mại đã có khả năng chế tạo các thiết bị RRAM, nhưng chủ yếu dành cho việc sử dụng bộ nhớ nhúng hơn là cho bộ nhớ máy tính. Một khi quy trình RRAM trở nên phổ biến rộng rãi hơn cho các nhà thiết kế vi mạch, một sản phẩm NeuRRAM có thể xảy ra. ”

Tuy nhiên, khó có thể dự đoán chính xác thời gian để điều này xảy ra, và Wan cho biết có thể là trong hai đến ba năm tới, hoặc lâu hơn nữa. ®

- AI

- nghệ thuật ai

- máy phát điện nghệ thuật ai

- ai rô bốt

- trí tuệ nhân tạo

- chứng nhận trí tuệ nhân tạo

- trí tuệ nhân tạo trong ngân hàng

- robot trí tuệ nhân tạo

- robot trí tuệ nhân tạo

- phần mềm trí tuệ nhân tạo

- blockchain

- hội nghị blockchain ai

- thiên tài

- trí tuệ nhân tạo đàm thoại

- hội nghị tiền điện tử ai

- dall's

- học kĩ càng

- google ai

- học máy

- plato

- Plato ai

- Thông tin dữ liệu Plato

- Trò chơi Plato

- PlatoDữ liệu

- Platogaming

- quy mô ai

- cú pháp

- Đăng ký

- zephyrnet