一篇新发表的研究论文描述了一种内存计算 (CIM) 芯片,该芯片将人工神经元与电阻式 RAM (RRAM) 相结合,从而可以在同一芯片上存储和处理 AI 模型权重。

该设计背后的研究人员声称,它对于边缘应用程序会更有效,因为它消除了单独的计算和内存块之间的数据移动。

至少在不久的将来,边缘计算和人工智能都有望迅速增长 根据分析公司IDC. 一些场景将它们结合在一起,因为边缘部署可能会受到功率和连接性的限制,但仍需要分析大量数据并对事件提供近乎实时的响应,从而使 AI 模型“生活”在设备中成为最佳解决方案.

有鉴于此,一组研究人员开发了一种称为 NeuRRAM 的芯片,因为它将人工神经元与 RRAM 结合在一种新颖的架构中。 该项目的目标是提供一种设计,该设计可以同时提供高能效以及支持各种人工智能模型的多功能性,以及与在软件中运行相同模型相当的准确性。

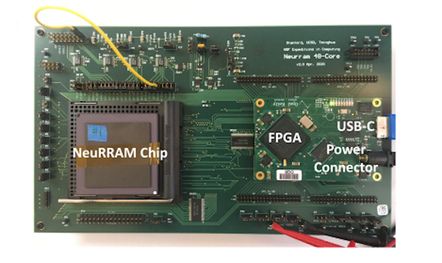

该项目最初是作为自然科学基金会项目“计算远征”的一部分开始的。 该项目汇集了来自不同机构、不同背景的研究人员,包括来自斯坦福大学和加州大学圣地亚哥分校的一些研究人员,以及中国清华大学的研究人员,他们是 RRAM 器件制造方面的专家。

能源效率:在电池供电的 Gizmo 上进行 AI 推理

斯坦福大学研究生研究员、研究人员之一万维尔表示。 论文作者昨天发表在 Nature 杂志上的 NeuRRAM 已被开发为一种 AI 芯片,可大大提高 AI 推理的能源效率,从而允许在智能可穿戴设备、无人机和工业 IoT 传感器等电池供电的边缘设备中直接实现复杂的 AI 功能.

“在今天的人工智能芯片中,数据处理和数据存储发生在不同的地方——计算单元和内存单元。 这些单元之间频繁的数据移动消耗的能量最多,成为实现边缘设备低功耗人工智能处理器的瓶颈,”他说。

为了解决这个问题,NeuRRAM 芯片实现了“内存计算”模型,其中处理直接在内存中进行。 它还利用了电阻式 RAM (RRAM),这是一种与静态 RAM 一样快但非易失性的存储器类型,允许它存储 AI 模型权重。 RRAM 单元的一个关键特性是神经权重可以作为不同的电导水平存储在存储单元中,通过数模转换器 (DAC) 进行编码并馈送到存储阵列。

这不是软件模拟,这是硬件

以前有关于 CIM 架构的研究,但这是第一次在硬件而不是软件模拟中展示广泛的 AI 应用程序,同时更节能并且能够准确地运行算法,这是以前的研究都没有的据万说,能够同时展示。

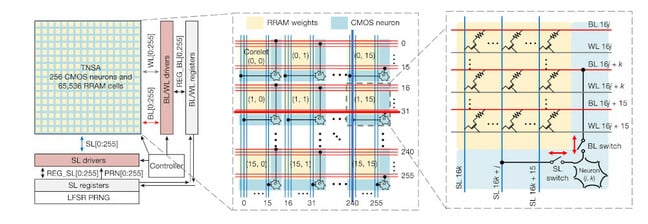

NeuRRAM 由 48 个 CIM 内核组成,总共包含 3 万个 RRAM 单元。 每个内核被描述为一个可转座神经突触阵列 (TNSA),由 256 × 256 RRAM 单元的网格和 256 个 CMOS 人工神经元电路组成,这些电路实现模数转换器 (ADC) 和激活功能。

根据该论文,TNSA 架构旨在提供对数据流方向的灵活控制,这对于支持具有不同数据流模式的各种 AI 模型至关重要。

例如,在视觉相关任务中常见的卷积神经网络 (CNN) 中,数据沿单个方向流过层以生成不同抽象级别的数据表示,而在其他一些模型中,概率采样在层之间来回执行直到网络收敛到高概率状态。

然而,其他将 CIM 与 RRAM 相结合的设计仅限于在单一方向上运行,通常是将 RRAM 交叉阵列的行和列硬连接到外围的专用电路以驱动输入和测量输出,该论文称。

产品思路

NeuRRAM 可重构性的秘诀在于它将 CMOS 神经元电路分布在 RRAM 单元之间,并沿行和列的长度将它们连接起来。

每个 TNSA 被分解成许多小核,每个小核由 16 × 16 RRAM 单元和一个神经元电路组成。 小核通过水平方向的共享位线 (BL) 和字线 (WL) 以及垂直方向的源极线 (SL) 连接。

神经元电路通过开关连接到通过 corelet 的 16 个中的一个 BL 和一个 SL,并负责整合来自连接到同一 BL 或 SL 的所有 256 个 RRAM 的输入。

每个神经元电路都可以使用其 BL 和 SL 开关进行输入和输出。 这意味着它可以通过开关从来自 BL 或 SL 的 RRAM 单元接收模拟矩阵矢量乘法 (MVM),但也可以通过相同的开关将转换后的数字结果发送到外围寄存器。

这种安排意味着可以通过配置在每个神经元电路的输入和输出阶段使用哪个开关来实现不同的数据流方向。

(这种架构也让我们想到了一些 SambaNova 的 AI 处理器芯片,它被实现为计算单元和内存单元的网格,由控制数据流的片上通信结构链接。)

该论文称,为了使用 NeuRRAM 中的 48 个 CIM 内核最大限度地提高 AI 推理性能,可以实施利用模型并行性和数据并行性的各种权重映射策略。

对于 CNN,策略可能是将早期、计算量最大的层的权重复制到多个 CIM 核心以进行并行推理。 本文对可用的权重映射策略进行了更详细的描述。

该论文报告了使用该芯片进行一系列 AI 任务的硬件测量推理结果,包括使用 CIFAR-10 和 MNIST 数据集的图像分类、谷歌语音命令识别和 MNIST 图像恢复,并使用各种 AI 模型实现。

据称,在所有这些基准任务中,它的推理精度可与使用 4 位权重训练的软件模型相媲美。 例如,它在使用 0.98 层 CNN 的 MNIST 手写数字识别上实现了 7% 的错误率,在使用 ResNet-14.34 的 CIFAR-10 对象分类上实现了 20% 的错误率,在使用15.34 细胞 LSTM(长期短期记忆)。

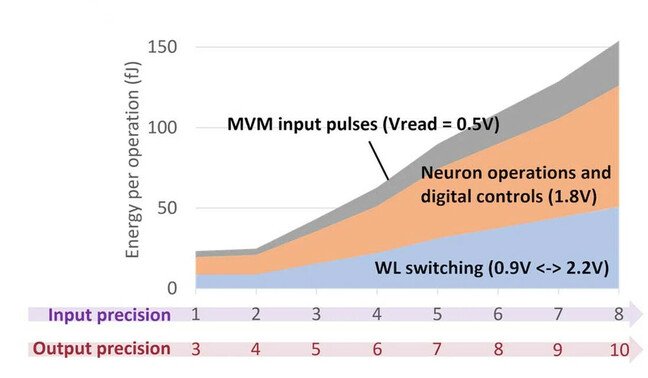

NeuRRAM 芯片还声称具有比使用 RRAM 的早期 CIM 芯片设计高两倍的能效,跨越各种计算位精度。 然而,论文中的能耗并没有以易于与市场上的商业设备进行比较的形式引用,下图显示了以飞焦(fJ)为单位测量的不同位精度下每次操作的能耗。

然而,Wan 告诉我们,对于当今在许多智能家居设备上运行的典型实时关键字定位任务(例如告诉智能扬声器打开灯),NeuRRAM 的功耗估计不到 2 微瓦。

“这意味着即使使用小型纽扣电池,它也可以运行 10 年以上(不考虑其他系统组件消耗的功率),”他说。

根据该论文,该芯片采用 130nm CMOS 技术制造,预计能效随着技术规模的扩大而提高,与其他半导体产品一样。

产品化还需要几年的时间

那么我们会看到基于这项技术的商业设备吗? 万说,它有很大的商业化潜力,并且个人正在考虑自己进行产品化。

“最合适的初始用例很可能是在极端边缘/物联网中,”他告诉我们。

与其他加速器一样,基于 NeuRRAM 芯片的产品可以与 CPU 组合在一个系统中,但这并不是每个应用程序都需要的。

“最近有一种趋势,即传感器的数据无需通过 CPU 或额外内存即可直接馈送到 AI 处理器,”Wan 说,但他补充说,对于大多数实际部署案例,此类 AI 加速器充当协处理器对于 CPU,CPU 管理其他任务。

NeuRRAM 芯片仅用于推理工作,很大程度上是因为当前形式的 RRAM 技术不太适合训练,因为训练过程需要频繁更新内存,而这是“对 RRAM 非常昂贵的操作”万说。

“目前,许多商业代工厂已经具备制造 RRAM 设备的能力,但主要用于嵌入式存储器,而不是用于内存计算。 一旦 RRAM 工艺为 IC 设计人员提供更广泛的应用,NeuRRAM 产品就可能出现。”

然而,这种情况发生的确切时间表很难预测,万说可能会在未来两到三年,甚至更长的时间内。 ®