Einleitung

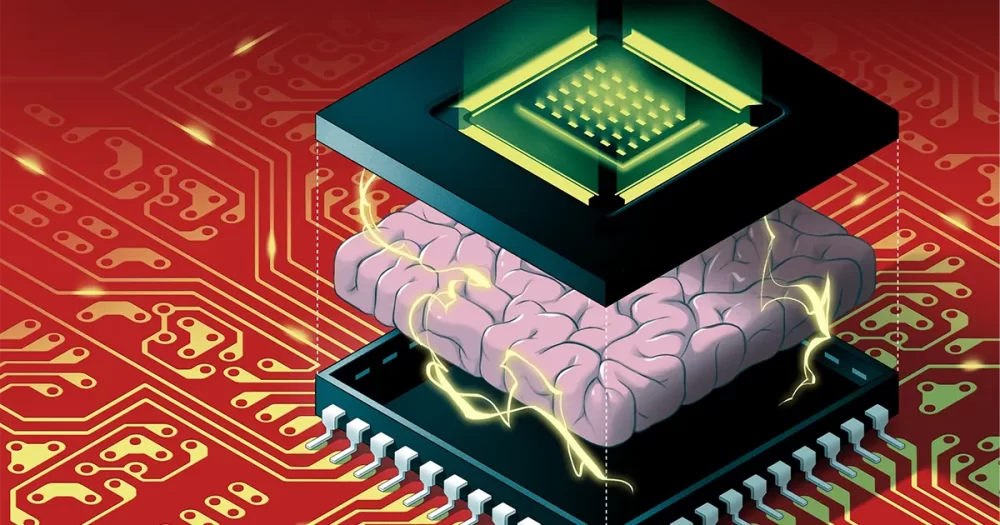

Algorithmen der künstlichen Intelligenz können nicht in ihrem derzeitigen Tempo wachsen. Algorithmen wie tiefe neuronale Netze – die lose vom Gehirn inspiriert sind, mit mehreren Schichten künstlicher Neuronen, die über numerische Werte, die als Gewichte bezeichnet werden, miteinander verbunden sind – werden jedes Jahr größer. Heutzutage halten Hardwareverbesserungen jedoch nicht mehr mit der enormen Menge an Speicher und Verarbeitungskapazität Schritt, die erforderlich ist, um diese massiven Algorithmen auszuführen. Bald könnte die Größe von KI-Algorithmen an eine Wand stoßen.

Und selbst wenn wir die Hardware weiter skalieren könnten, um den Anforderungen der KI gerecht zu werden, gibt es ein weiteres Problem: Der Betrieb auf herkömmlichen Computern verschwendet enorm viel Energie. Die hohen COXNUMX-Emissionen, die durch den Betrieb großer KI-Algorithmen entstehen, sind bereits schädlich für die Umwelt, und es wird noch schlimmer, wenn die Algorithmen immer gigantischer werden.

Eine Lösung namens Neuromorphic Computing lässt sich von biologischen Gehirnen inspirieren, um energieeffiziente Designs zu erstellen. Obwohl diese Chips digitale Computer beim Energiesparen überflügeln können, fehlt ihnen leider die Rechenleistung, die für den Betrieb eines beträchtlichen tiefen neuronalen Netzwerks erforderlich ist. Das macht sie für KI-Forscher leicht zu übersehen.

Das änderte sich schließlich im August, als Weier Wan, H.-S. Philipp Wong, Gert Cauwenberghs und ihre Kollegen enthüllte einen neuen neuromorphen Chip NeuRRAM genannt, das 3 Millionen Speicherzellen und Tausende von Neuronen enthält, die in seine Hardware eingebaut sind, um Algorithmen auszuführen. Es verwendet einen relativ neuen Speichertyp namens resistives RAM oder RRAM. Im Gegensatz zu früheren RRAM-Chips ist NeuRRAM so programmiert, dass es analog arbeitet, um mehr Energie und Platz zu sparen. Während der digitale Speicher binär ist und entweder eine 1 oder 0 speichert, können analoge Speicherzellen im NeuRRAM-Chip jeweils mehrere Werte entlang eines vollständig kontinuierlichen Bereichs speichern. Dadurch kann der Chip mehr Informationen von massiven KI-Algorithmen auf der gleichen Chipfläche speichern.

Infolgedessen kann der neue Chip bei komplexen KI-Aufgaben wie Bild- und Spracherkennung so gut wie digitale Computer arbeiten, und die Autoren behaupten, dass er bis zu 1,000-mal energieeffizienter ist, was winzigen Chips die Möglichkeit eröffnet, immer kompliziertere Algorithmen auszuführen in kleinen Geräten, die zuvor für KI ungeeignet waren, wie Smart Watches und Telefone.

Forscher, die nicht an der Arbeit beteiligt waren, waren von den Ergebnissen tief beeindruckt. "Dieses Papier ist ziemlich einzigartig", sagte er Zhongrui Wang, ein langjähriger RRAM-Forscher an der Universität von Hongkong. „Es leistet Beiträge auf verschiedenen Ebenen – auf der Geräteebene, auf der Ebene der Schaltungsarchitektur und auf der Ebene der Algorithmen.“

Neue Erinnerungen schaffen

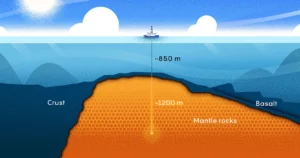

Bei digitalen Computern wird die enorme Energieverschwendung beim Ausführen von KI-Algorithmen durch einen einfachen und allgegenwärtigen Konstruktionsfehler verursacht, der jede einzelne Berechnung ineffizient macht. Typischerweise wird der Speicher eines Computers – der die Daten und numerischen Werte enthält, die er während der Berechnung verarbeitet – auf der Hauptplatine abseits des Prozessors platziert, wo die Berechnung stattfindet.

Für die Informationen, die durch den Prozessor fließen, „ist es so, als ob Sie acht Stunden mit dem Pendeln verbringen, aber zwei Stunden arbeiten“, sagte Wan, ein Informatiker, der früher an der Stanford University war und kürzlich zum KI-Startup Aizip gewechselt ist.

Einleitung

Dieses Problem mit neuen All-in-One-Chips zu beheben, die Speicher und Berechnung am selben Ort platzieren, scheint einfach zu sein. Es ist auch näher daran, wie unser Gehirn wahrscheinlich Informationen verarbeitet, da viele Neurowissenschaftler glauben, dass Berechnungen innerhalb von Populationen von Neuronen stattfinden, während Erinnerungen gebildet werden, wenn die Synapsen zwischen Neuronen ihre Verbindungen stärken oder schwächen. Die Herstellung solcher Geräte hat sich jedoch als schwierig erwiesen, da aktuelle Speicherformen mit der Technologie in Prozessoren nicht kompatibel sind.

Informatiker haben vor Jahrzehnten die Materialien entwickelt, um neue Chips herzustellen, die Berechnungen dort durchführen, wo Speicher gespeichert ist – eine Technologie, die als Compute-in-Memory bekannt ist. Aber da traditionelle digitale Computer so gut funktionieren, wurden diese Ideen jahrzehntelang übersehen.

„Diese Arbeit geriet, wie die meisten wissenschaftlichen Arbeiten, irgendwie in Vergessenheit“, sagte Wong, Professor an der Stanford University.

Tatsächlich ist die erstes solches Gerät geht mindestens auf das Jahr 1964 zurück, als Elektroingenieure in Stanford entdeckten, dass sie bestimmte Materialien, sogenannte Metalloxide, manipulieren konnten, um ihre Fähigkeit, Elektrizität zu leiten, ein- und auszuschalten. Das ist von Bedeutung, da die Fähigkeit eines Materials, zwischen zwei Zuständen umzuschalten, das Rückgrat für die herkömmliche Speicherung darstellt. Typischerweise entspricht in digitalen Speichern ein Zustand hoher Spannung einer 1 und einer niedrigen Spannung einer 0.

Um ein RRAM-Gerät dazu zu bringen, den Zustand zu wechseln, legen Sie eine Spannung an Metallelektroden an, die an zwei Enden des Metalloxids angeschlossen sind. Normalerweise sind Metalloxide Isolatoren, was bedeutet, dass sie keinen Strom leiten. Aber mit genügend Spannung baut sich der Strom auf, drückt sich schließlich durch die Schwachstellen des Materials und bahnt sich einen Weg zur Elektrode auf der anderen Seite. Sobald der Strom durchgebrochen ist, kann er auf diesem Weg frei fließen.

Wong vergleicht diesen Vorgang mit einem Blitz: Wenn sich in einer Wolke genügend Ladung aufgebaut hat, findet sie schnell einen niederohmigen Weg und Blitze schlagen ein. Aber anders als beim Blitz, dessen Weg verschwindet, bleibt der Weg durch das Metalloxid bestehen, das heißt, es bleibt unbegrenzt leitfähig. Und es ist möglich, die Leiterbahn zu löschen, indem man eine andere Spannung an das Material anlegt. Forscher können also einen RRAM zwischen zwei Zuständen umschalten und sie zum Speichern digitaler Speicher verwenden.

Die Forscher der Mitte des Jahrhunderts erkannten das Potenzial für energieeffizientes Rechnen nicht und brauchten es bei den kleineren Algorithmen, mit denen sie arbeiteten, noch nicht. Es dauerte bis in die frühen 2000er Jahre, als Forscher neue Metalloxide entdeckten, um die Möglichkeiten zu erkennen.

Wong, der damals bei IBM arbeitete, erinnert sich, dass ein preisgekrönter Kollege, der an RRAM arbeitete, zugab, dass er die beteiligten physikalischen Zusammenhänge nicht vollständig verstand. „Wenn er es nicht versteht“, erinnert sich Wong, dachte er, „sollte ich vielleicht nicht versuchen, es zu verstehen.“

Aber im Jahr 2004 gaben Forscher von Samsung Electronics bekannt, dass sie es getan hatten erfolgreich integrierter RRAM-Speicher auf einem herkömmlichen Computerchip aufgebaut, was darauf hindeutet, dass ein Compute-in-Memory-Chip endlich möglich sein könnte. Wong beschloss, es zumindest zu versuchen.

Compute-in-Memory-Chips für KI

Mehr als ein Jahrzehnt lang haben Forscher wie Wong daran gearbeitet, die RRAM-Technologie so weit aufzubauen, dass sie leistungsstarke Rechenaufgaben zuverlässig bewältigen kann. Um 2015 begannen Informatiker das enorme Potenzial dieser energieeffizienten Geräte für große KI-Algorithmen zu erkennen, die sich zu entfalten begannen. In diesem Jahr, Wissenschaftler an der University of California, Santa Barbara zeigte dass RRAM-Geräte mehr können, als nur Speicher auf neue Weise zu speichern. Sie könnten grundlegende Rechenaufgaben selbst ausführen – einschließlich der überwiegenden Mehrheit der Berechnungen, die innerhalb der künstlichen Neuronen eines neuronalen Netzwerks stattfinden, bei denen es sich um einfache Matrixmultiplikationsaufgaben handelt.

Im NeuRRAM-Chip sind Siliziumneuronen in die Hardware eingebaut, und die RRAM-Speicherzellen speichern die Gewichtungen – die Werte, die die Stärke der Verbindungen zwischen Neuronen darstellen. Und da die NeuRRAM-Speicherzellen analog sind, repräsentieren die Gewichte, die sie speichern, den gesamten Bereich der Widerstandszustände, die auftreten, wenn das Gerät zwischen einem niederohmigen und einem hochohmigen Zustand umschaltet. Dies ermöglicht eine noch höhere Energieeffizienz als digitale RRAM-Speicher erreichen können, da der Chip viele Matrixberechnungen parallel ausführen kann – und nicht im Gleichschritt nacheinander, wie in den Versionen mit digitaler Verarbeitung.

Da die analoge Verarbeitung jedoch immer noch Jahrzehnte hinter der digitalen Verarbeitung zurückbleibt, gibt es noch viele Probleme zu beseitigen. Einer davon ist, dass analoge RRAM-Chips ungewöhnlich präzise sein müssen, da Unvollkommenheiten auf dem physischen Chip zu Schwankungen und Rauschen führen können. (Bei herkömmlichen Chips mit nur zwei Zuständen spielen diese Unvollkommenheiten nicht annähernd so eine Rolle.) Das macht es für analoge RRAM-Geräte erheblich schwieriger, KI-Algorithmen auszuführen, da die Genauigkeit beispielsweise der Erkennung eines Bildes darunter leidet Der leitende Zustand des RRAM-Geräts ist nicht jedes Mal genau gleich.

„Wenn wir uns einen Lichtweg ansehen, ist er jedes Mal anders“, sagte Wong. „Infolgedessen weist das RRAM ein gewisses Maß an Stochastik auf – jedes Mal, wenn Sie es programmieren, ist es etwas anders.“ Wong und seine Kollegen haben bewiesen, dass RRAM-Geräte kontinuierliche KI-Gewichte speichern und dennoch so genau wie digitale Computer sein können, wenn die Algorithmen darauf trainiert sind, sich an das Rauschen zu gewöhnen, auf das sie auf dem Chip stoßen, ein Fortschritt, der es ihnen ermöglichte, den NeuRRAM-Chip herzustellen.

Einleitung

Ein weiteres wichtiges Problem, das sie lösen mussten, betraf die Flexibilität, die zur Unterstützung verschiedener neuronaler Netze erforderlich ist. In der Vergangenheit mussten Chipdesigner die winzigen RRAM-Bausteine in einem Bereich neben größeren Silizium-Neuronen anordnen. Die RRAM-Geräte und die Neuronen waren ohne Programmierbarkeit fest verdrahtet, sodass die Berechnung nur in einer einzigen Richtung durchgeführt werden konnte. Um neuronale Netze mit bidirektionaler Berechnung zu unterstützen, waren zusätzliche Drähte und Schaltkreise erforderlich, was den Energie- und Platzbedarf aufblähte.

Also entwarf Wongs Team eine neue Chiparchitektur, bei der die RRAM-Speicherbausteine und Siliziumneuronen miteinander vermischt wurden. Diese kleine Änderung am Design reduzierte die Gesamtfläche und sparte Energie.

„Ich fand [das Arrangement] wirklich schön“, sagte er Melika Payvand, Neuromorphiker an der Eidgenössischen Technischen Hochschule Zürich. „Ich halte es definitiv für eine bahnbrechende Arbeit.“

Mehrere Jahre lang arbeitete Wongs Team mit Mitarbeitern zusammen, um KI-Algorithmen auf dem NeuRRAM-Chip zu entwerfen, herzustellen, zu testen, zu kalibrieren und auszuführen. Sie erwogen die Verwendung anderer neuer Speichertypen, die auch in einem Compute-in-Memory-Chip verwendet werden können, aber RRAM hatte einen Vorteil aufgrund seiner Vorteile bei der analogen Programmierung und weil es relativ einfach in herkömmliche Computermaterialien zu integrieren war.

Ihre jüngsten Ergebnisse stellen den ersten RRAM-Chip dar, der so große und komplexe KI-Algorithmen ausführen kann – eine Leistung, die bisher nur in theoretischen Simulationen möglich war. „Wenn es um echtes Silizium geht, fehlte diese Fähigkeit“, sagte er Anup Das, Informatiker an der Drexel University. „Diese Arbeit ist die erste Demonstration.“

„Digitale KI-Systeme sind flexibel und präzise, aber um Größenordnungen weniger effizient“, sagt Cauwenberghs. Jetzt, so Cauwenberghs, habe ihr flexibler, präziser und energieeffizienter analoger RRAM-Chip „zum ersten Mal die Lücke geschlossen“.

Hochskalieren

Das Design des Teams hält den NeuRRAM-Chip winzig – gerade so groß wie ein Fingernagel – während 3 Millionen RRAM-Speicherbausteine zusammengedrückt werden, die als analoge Prozessoren dienen können. Und obwohl er neuronale Netze mindestens so gut ausführen kann wie digitale Computer, kann der Chip auch (und zum ersten Mal) Algorithmen ausführen, die Berechnungen in verschiedene Richtungen durchführen. Ihr Chip kann eine Spannung in die Zeilen des RRAM-Arrays eingeben und Ausgaben aus den Spalten lesen, wie es für RRAM-Chips üblich ist, aber er kann dies auch rückwärts von den Spalten zu den Zeilen tun, sodass er in funktionierenden neuronalen Netzwerken verwendet werden kann mit Datenfluss in verschiedene Richtungen.

Wie bei der RRAM-Technologie selbst ist dies seit langem möglich, aber niemand hat daran gedacht. „Warum haben wir nicht schon früher darüber nachgedacht?“ fragte Payvand. „Im Nachhinein weiß ich es nicht.“

„Das eröffnet tatsächlich viele andere Möglichkeiten“, sagte Das. Als Beispiele nannte er die Fähigkeit eines einfachen Systems, die enormen Algorithmen auszuführen, die für multidimensionale Physiksimulationen oder selbstfahrende Autos benötigt werden.

Größe ist jedoch ein Problem. Die größten neuronalen Netze enthalten jetzt Milliarden von Gewichten, nicht die Millionen, die in den neuen Chips enthalten sind. Wong plant eine Skalierung, indem er mehrere NeuRRAM-Chips übereinander stapelt.

Ebenso wichtig wird es sein, die Energiekosten zukünftiger Geräte niedrig zu halten oder noch weiter zu skalieren. Ein Weg dorthin führt über Kopieren des Gehirns das Kommunikationssignal, das zwischen echten Neuronen verwendet wird, noch genauer zu übernehmen: die elektrische Spitze. Es ist ein Signal, das von einem Neuron zum anderen abgefeuert wird, wenn der Spannungsunterschied zwischen dem Inneren und dem Äußeren der Zelle einen kritischen Schwellenwert erreicht.

„Da gibt es große Herausforderungen“, sagte er Toni Kenyon, ein Nanotechnologieforscher am University College London. „Aber vielleicht möchten wir trotzdem in diese Richtung gehen, denn … die Chancen stehen gut, dass Sie eine größere Energieeffizienz haben, wenn Sie sehr spärliche Spikes verwenden.“ Um Algorithmen mit Spikes auf dem aktuellen NeuRRAM-Chip auszuführen, wäre jedoch wahrscheinlich eine völlig andere Architektur erforderlich, bemerkte Kenyon.

Vorerst hat die Energieeffizienz, die das Team beim Ausführen großer KI-Algorithmen auf dem NeuRRAM-Chip erzielte, neue Hoffnung geweckt, dass Speichertechnologien die Zukunft des Rechnens mit KI darstellen könnten. Vielleicht können wir es eines Tages sogar mit den 86 Milliarden Neuronen des menschlichen Gehirns und den Billionen von Synapsen, die sie verbinden, aufnehmen, ohne dass uns die Energie ausgeht.