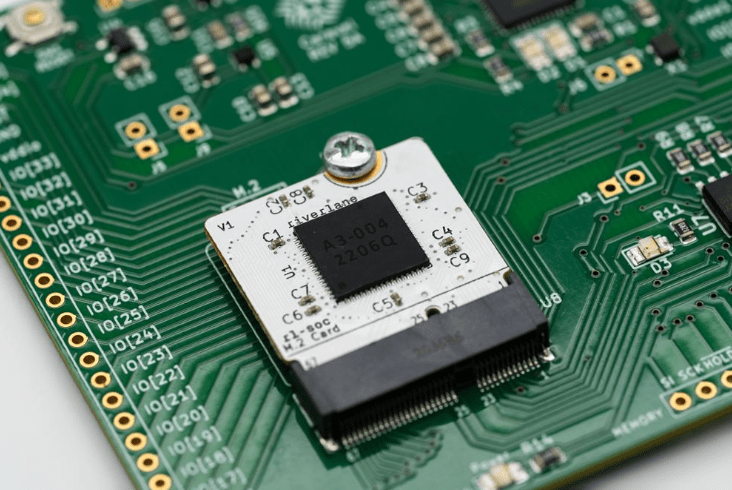

A medida que el sector de la computación cuántica continúa enfocándose en mejorar la fidelidad y las tasas de error, Riverlane anunció su chip decodificador demostrador ASIC dedicado para predecir y corregir errores, y publicó su IP decodificador y un artículo sobre corrección de errores eficiente en recursos para computadoras cuánticas.

Las medidas representan un importante paso adelante en el esfuerzo continuo de la compañía para construir la pila de corrección de errores cuánticos que Riverlane y otros han argumentado que cada computadora cuántica necesitará para alcanzar una escala útil.

Steve Brierley, director ejecutivo y fundador de Riverlane, dijo: “Estamos entrando en una nueva era de la computación cuántica en la que comenzamos a abordar el desafío que define la tecnología: la necesidad de escalar desde unos pocos cientos de operaciones cuánticas hasta un billón de operaciones cuánticas sin fallas.

Riverlane planea demostrar el ASIC DD0A, el primero de su familia Decode ASIC planificada, en hardware en vivo en el cuarto trimestre de este año, mientras que la publicación del IP del decodificador DD1 permite una rápida integración y creación de prototipos, lo que significa que la tecnología de corrección de errores puede se implementará en una FPGA para que los fabricantes de computadoras cuánticas la incorporen a su propio hardware.

"Implementamos nuestro decodificador tanto en una FPGA como en un ASIC; este último es, en última instancia, necesario para cualquier solución escalable rentable", afirma el artículo de investigación de la empresa.

Las nuevas soluciones se pueden integrar en hardware cuántico superconductor, de iones atrapados y de átomos neutros, dijo Riverlane.

Brierley añadió: “Ahora estamos implementando algoritmos cuánticos en hardware real. Fundamentalmente, Riverlane ha encontrado un equilibrio para abordar todas las métricas necesarias para crear un decodificador del mundo real para resolver problemas del mundo real, lo que convierte a nuestro decodificador en el más potente disponible”.

Riverlane elevado $ 18.7 millones en nuevos fondos en abril de este año.

Dan O'Shea ha cubierto telecomunicaciones y temas relacionados, incluidos semiconductores, sensores, sistemas minoristas, pagos digitales y computación/tecnología cuántica durante más de 25 años.

- Distribución de relaciones públicas y contenido potenciado por SEO. Consiga amplificado hoy.

- PlatoData.Network Vertical Generativo Ai. Empodérate. Accede Aquí.

- PlatoAiStream. Inteligencia Web3. Conocimiento amplificado. Accede Aquí.

- PlatoESG. Carbón, tecnología limpia, Energía, Ambiente, Solar, Gestión de residuos. Accede Aquí.

- PlatoSalud. Inteligencia en Biotecnología y Ensayos Clínicos. Accede Aquí.

- Desplazamientos de bloque. Modernización de la propiedad de compensaciones ambientales. Accede Aquí.

- Fuente: https://www.insidequantumtechnology.com/news-archive/riverlane-unveils-decoder-chip-in-step-toward-error-correction-stack/

- :posee

- :dónde

- 2023

- 25

- 7

- a

- Lograr

- real

- adicional

- dirección

- algoritmos

- Todos

- permite

- an

- y

- anunció

- cualquier

- Abril

- somos

- argumentó

- ASIC

- átomo

- Hoy Disponibles

- Balance

- BE

- comenzar

- "Ser"

- ambas

- build

- by

- PUEDEN

- ceo

- CEO

- Reto

- chip

- De la empresa

- computadora

- computadoras

- informática

- continúa

- rentable

- cubierto

- Para crear

- crucialmente

- a dedicados

- definir

- demostrar

- desplegado

- digital

- Pagos digitales

- esfuerzo

- que entran a los

- Era

- error

- Errores

- Cada

- Fracaso

- familia

- pocos

- fidelidad

- Nombre

- Focus

- adelante

- encontrado

- fundador

- Cuarto

- FPGA

- Desde

- Materiales

- Tienen

- Alta

- HTTPS

- cien

- imagen

- implementar

- implementación

- la mejora de

- in

- Incluye

- incorporar

- dentro

- Dentro de la tecnología cuántica

- COMPLETAMENTE

- integración

- dentro

- IP

- SUS

- para vivir

- Makers

- Realizar

- max-ancho

- sentido

- Métrica

- millones

- MEJOR DE TU

- se mueve

- necesario

- ¿ Necesita ayuda

- Neutro

- Nuevo

- ahora

- of

- on

- en marcha

- Operaciones

- Otros

- nuestros

- salir

- Más de

- EL DESARROLLADOR

- Papel

- pagos

- planificado

- jubilación

- Platón

- Inteligencia de datos de Platón

- PlatónDatos

- publicado

- poderoso

- predecir

- problemas

- prototipado

- publicado

- DTP

- Cuántico

- algoritmos cuánticos

- Computadora cuántica

- computadoras cuánticas

- computación cuántica

- corrección de error cuántico

- tecnología cuántica

- Trimestre

- Búsqueda

- elevado

- Tarifas

- mundo real

- relacionado

- representar

- Requisitos

- la investigación

- el comercio minorista

- carril fluvial

- Said

- escalable

- Escala

- sector

- Semiconductores

- sensor

- importante

- a medida

- Soluciones

- RESOLVER

- montón

- dijo

- paso

- superconductor

- Todas las funciones a su disposición

- abordando

- Tecnología

- telecomunicaciones

- esa

- La

- su

- así

- este año

- a

- Temas

- hacia

- Trillones

- verdadero

- Finalmente, a veces

- Revela

- we

- mientras

- seguirá

- sin

- año

- años

- zephyrnet