कभी भी बड़े एआई और मशीन लर्निंग मॉडल की प्यास बुझाने के लिए, टेस्ला ने हॉट चिप्स 34 में डोजो नामक अपने पूरी तरह से कस्टम सुपरकंप्यूटिंग आर्किटेक्चर पर विवरणों का खजाना प्रकट किया है।

सिस्टम अनिवार्य रूप से एक विशाल कंपोज़ेबल सुपरकंप्यूटर है, हालांकि हम जो देखते हैं उसके विपरीत शीर्ष 500, यह पूरी तरह से कस्टम आर्किटेक्चर से बनाया गया है जो कंप्यूट, नेटवर्किंग और इनपुट/आउटपुट (I/O) सिलिकॉन से लेकर इंस्ट्रक्शन सेट आर्किटेक्चर (ISA), पावर डिलीवरी, पैकेजिंग और कूलिंग तक फैला हुआ है। यह सब बड़े पैमाने पर सिलवाया, विशिष्ट मशीन लर्निंग ट्रेनिंग एल्गोरिदम चलाने के स्पष्ट उद्देश्य के साथ किया गया था।

टेस्ला में हार्डवेयर इंजीनियरिंग के वरिष्ठ निदेशक गणेश वेंकटरमणन ने कहा, "वास्तविक दुनिया की डेटा प्रोसेसिंग केवल मशीन लर्निंग तकनीकों के माध्यम से संभव है, चाहे वह प्राकृतिक-भाषा प्रसंस्करण हो, सड़कों पर ड्राइविंग जो मानव दृष्टि के लिए रोबोटिक्स के लिए बनाई गई हो, जो रोजमर्रा के वातावरण के साथ इंटरफेसिंग करती हो।" अपने मुख्य भाषण के दौरान।

हालांकि, उन्होंने तर्क दिया कि वितरित कार्यभार को बढ़ाने के पारंपरिक तरीके मशीन लर्निंग की मांगों को पूरा करने के लिए आवश्यक दर पर तेजी लाने में विफल रहे हैं। वास्तव में, मूर का नियम इसमें कटौती नहीं कर रहा है और न ही एआई/एमएल प्रशिक्षण के लिए बड़े पैमाने पर सिस्टम उपलब्ध हैं, अर्थात् सीपीयू/जीपीयू के कुछ संयोजन या विशेष एआई त्वरक का उपयोग करके दुर्लभ परिस्थितियों में।

"परंपरागत रूप से हम चिप्स बनाते हैं, हम उन्हें पैकेज पर डालते हैं, पैकेज पीसीबी पर जाते हैं, जो सिस्टम में जाते हैं। सिस्टम रैक में जाते हैं, ”वेंकटरामन ने कहा। समस्या यह है कि हर बार जब डेटा चिप से पैकेज में जाता है और पैकेज से बाहर होता है, तो यह विलंबता और बैंडविड्थ जुर्माना लगाता है।

एक डाटासेंटर सैंडविच

इसलिए सीमाओं को पार करने के लिए, वेंकटरमणन और उनकी टीम ने नए सिरे से शुरुआत की।

"एलोन के साथ मेरे साक्षात्कार के ठीक बाद, उन्होंने मुझसे पूछा कि आप ऐसा क्या कर सकते हैं जो एआई के लिए सीपीयू और जीपीयू से अलग है। मुझे लगता है कि पूरी टीम अभी भी इस सवाल का जवाब दे रही है।”

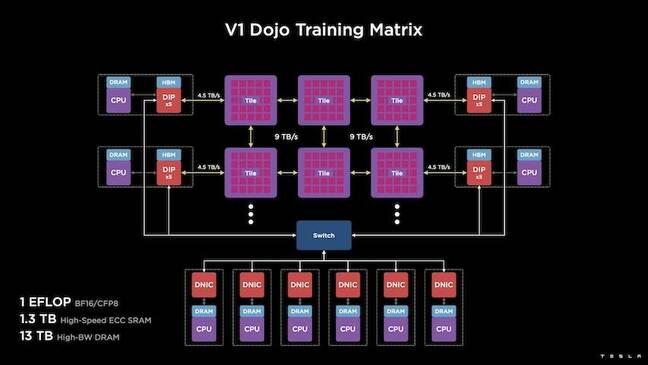

इससे डोजो ट्रेनिंग टाइल का विकास हुआ, जो एक स्व-निहित कंप्यूट क्लस्टर है, जो 556kW लिक्विड-कूल्ड पैकेज में FP32 के प्रदर्शन के 15 TFLOPS में सक्षम आधा-घन फुट पर कब्जा कर लेता है।

प्रत्येक टाइल 11GB SRAM से लैस है और पूरे स्टैक में एक कस्टम ट्रांसपोर्ट प्रोटोकॉल का उपयोग करके 9TB/s फैब्रिक से जुड़ा है।

वेंकटरमन ने कहा, "यह प्रशिक्षण टाइल बिना किसी अतिरिक्त स्विच की आवश्यकता के, कंप्यूटर से मेमोरी से पावर डिलीवरी, संचार के लिए एकीकरण की अद्वितीय मात्रा का प्रतिनिधित्व करती है।"

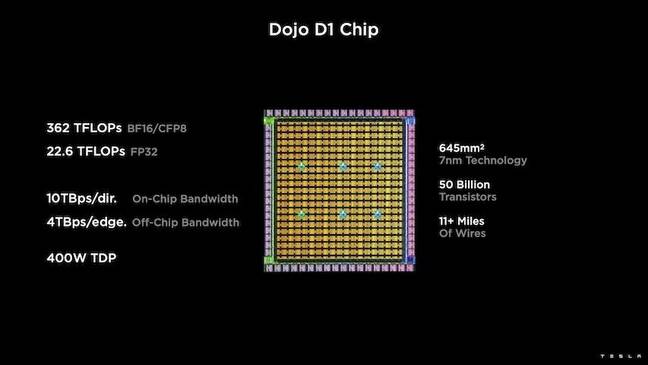

प्रशिक्षण टाइल के केंद्र में TSMC की 1nm प्रक्रिया के आधार पर, टेस्ला का D50 है, जो 7 बिलियन का ट्रांजिस्टर डाई है। टेस्ला का कहना है कि प्रत्येक D1 22W के TDP पर FP32 प्रदर्शन के 400 TFLOPS में सक्षम है। हालाँकि, टेस्ला ने नोट किया कि चिप कुछ कस्टम वाले सहित फ्लोटिंग पॉइंट गणनाओं की एक विस्तृत श्रृंखला को चलाने में सक्षम है।

वेंकटरमन ने कहा, "यदि आप मिलीमीटर वर्ग के लिए ट्रांजिस्टर की तुलना करते हैं, तो शायद यह किसी भी चीज का खून बह रहा किनारा है।"

टेस्ला ने तब 25 D1s लिए, उन्हें ज्ञात अच्छे मरने के लिए रखा, और फिर उन्हें TSMC की सिस्टम-ऑन-वेफर तकनीक का उपयोग करके "बहुत कम विलंबता और बहुत उच्च बैंडविड्थ पर गणना एकीकरण की एक बड़ी मात्रा प्राप्त करने के लिए" पैक किया, उन्होंने कहा।

हालाँकि, सिस्टम-ऑन-वेफर डिज़ाइन और लंबवत स्टैक्ड आर्किटेक्चर ने जब बिजली वितरण की बात की तो चुनौतियों का सामना करना पड़ा।

वेंकटरमणन के अनुसार, अधिकांश त्वरक आज बिजली को सीधे सिलिकॉन से सटे हुए रखते हैं। और सिद्ध होने पर, इस दृष्टिकोण का अर्थ है कि त्वरक का एक बड़ा क्षेत्र उन घटकों को समर्पित होना चाहिए, जिसने इसे डोजो के लिए अव्यवहारिक बना दिया, उन्होंने समझाया। इसके बजाय, टेस्ला ने अपने चिप्स को सीधे बिजली देने के लिए डिज़ाइन किया, हालांकि मरने के नीचे।

सब एक साथ रखना

"हम इस प्रशिक्षण टाइल से एक संपूर्ण डेटासेंटर या पूरी इमारत बना सकते हैं, लेकिन प्रशिक्षण टाइल केवल गणना भाग है। हमें इसे खिलाने की भी जरूरत है, ”वेंकटरामन ने कहा।

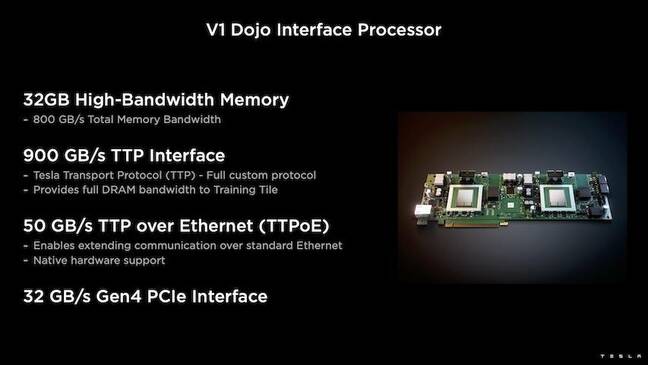

इसके लिए टेस्ला ने डोजो इंटरफेस प्रोसेसर (डीआईपी) भी विकसित किया, जो होस्ट सीपीयू और ट्रेनिंग प्रोसेसर के बीच सेतु का काम करता है। डीआईपी साझा उच्च-बैंडविड्थ मेमोरी (एचबीएम) के स्रोत के रूप में और उच्च गति 400 जीबी/सेकंड एनआईसी के रूप में भी कार्य करता है।

प्रत्येक डीआईपी में 32जीबी का एचबीएम होता है और इनमें से पांच कार्डों को 900जीबी/एस पर एक प्रशिक्षण टाइल से जोड़ा जा सकता है, जो कुल 4.5 टीबी/एस के लिए मेजबान को कुल 160 जीबी एचबीएम प्रति टाइल के लिए दिया जा सकता है।

इन टाइलों के टेस्ला के V1 कॉन्फ़िगरेशन जोड़े - या 150 D1 मर जाते हैं - सरणी में चार होस्ट CPUs समर्थित हैं जिनमें से प्रत्येक में BF16 या CF8 प्रदर्शन का दावा किया गया एक्साफ्लॉप प्राप्त करने के लिए पांच डीआईपी कार्ड हैं।

एक साथ रखो, वेंकटरमण कहते हैं वास्तुकला - विस्तृत यहाँ गहराई में by अगला प्लेटफार्म - टेस्ला को एनवीडिया और एएमडी की पसंद से पारंपरिक त्वरक से जुड़ी सीमाओं को दूर करने में सक्षम बनाता है।

"पारंपरिक त्वरक कैसे काम करते हैं, आम तौर पर आप प्रत्येक त्वरक में एक संपूर्ण मॉडल फिट करने का प्रयास करते हैं। इसे दोहराएं, और फिर उनमें से प्रत्येक के माध्यम से डेटा प्रवाहित करें, ”उन्होंने कहा। "अगर हमारे पास बड़े और बड़े मॉडल हों तो क्या होगा? ये त्वरक गिर सकते हैं क्योंकि वे स्मृति से बाहर हो जाते हैं।"

उन्होंने कहा कि यह कोई नई समस्या नहीं है। उदाहरण के लिए एनवीडिया का एनवी-स्विच मेमोरी को जीपीयू के बड़े बैंकों में जमा करने में सक्षम बनाता है। हालांकि, वेंकटरमन का तर्क है कि यह न केवल जटिलता जोड़ता है, बल्कि विलंबता का परिचय देता है और बैंडविड्थ पर समझौता करता है।

"हमने इस बारे में शुरुआत से ही सोचा था। हमारी गणना टाइलें और प्रत्येक डाई बड़े मॉडल की फिटिंग के लिए बनाई गई थी, ”वेंकटरामन ने कहा।

सॉफ्टवेयर

इस तरह की एक विशेष गणना वास्तुकला एक विशेष सॉफ्टवेयर स्टैक की मांग करती है। हालांकि, वेंकटरमणन और उनकी टीम ने माना कि प्रोग्राम योग्यता डोजो को या तो बना देगी या तोड़ देगी।

"जब हम इन प्रणालियों को डिजाइन करते हैं, तो सॉफ्टवेयर समकक्षों के लिए प्रोग्राम योग्यता में आसानी सर्वोपरि है," उन्होंने कहा। "शोधकर्ता आपके सॉफ़्टवेयर लोगों के लिए एक नए एल्गोरिदम को अपनाने के लिए हस्तलिखित कर्नेल लिखने की प्रतीक्षा नहीं करेंगे जिसे हम चलाना चाहते हैं।"

ऐसा करने के लिए, टेस्ला ने गुठली का उपयोग करने के विचार को त्याग दिया, और डोजो की वास्तुकला को संकलक के आसपास डिजाइन किया।

"हमने जो किया वह हमने PiTorch का इस्तेमाल किया था। हमने एक मध्यवर्ती परत बनाई, जो हमें इसके नीचे हार्डवेयर को समानांतर बनाने में मदद करती है। नीचे सब कुछ संकलित कोड है, ”उन्होंने कहा। "सॉफ्टवेयर स्टैक बनाने का यही एकमात्र तरीका है जो उन सभी भविष्य के वर्कलोड के अनुकूल है।"

सॉफ्टवेयर लचीलेपन पर जोर देने के बावजूद, वेंकटरमन ने नोट किया कि प्लेटफॉर्म, जो वर्तमान में उनकी प्रयोगशालाओं में चल रहा है, फिलहाल टेस्ला के उपयोग तक सीमित है।

"हम पहले अपने आंतरिक ग्राहकों पर ध्यान केंद्रित कर रहे हैं," उन्होंने कहा। "एलोन ने इसे सार्वजनिक कर दिया है कि समय के साथ, हम इसे शोधकर्ताओं के लिए उपलब्ध करा देंगे, लेकिन हमारे पास इसके लिए कोई समय सीमा नहीं है। ®

- AI

- ai कला

- ऐ कला जनरेटर

- ऐ रोबोट

- कृत्रिम बुद्धिमत्ता

- कृत्रिम बुद्धिमत्ता प्रमाणन

- बैंकिंग में आर्टिफिशियल इंटेलिजेंस

- आर्टिफिशियल इंटेलिजेंस रोबोट

- आर्टिफिशियल इंटेलिजेंस रोबोट

- कृत्रिम बुद्धि सॉफ्टवेयर

- blockchain

- ब्लॉकचेन सम्मेलन एआई

- कॉइनजीनियस

- संवादी कृत्रिम बुद्धिमत्ता

- क्रिप्टो सम्मेलन एआई

- दल-ए

- ध्यान लगा के पढ़ना या सीखना

- इसे गूगल करें

- यंत्र अधिगम

- प्लेटो

- प्लेटो एआई

- प्लेटो डेटा इंटेलिजेंस

- प्लेटो गेम

- प्लेटोडाटा

- प्लेटोगेमिंग

- स्केल एआई

- वाक्यविन्यास

- रजिस्टर

- जेफिरनेट