En nyligen publicerad forskningsartikel beskriver ett compute-in-memory (CIM)-chip som kombinerar artificiella neuroner med resistivt RAM (RRAM) så att AI-modellvikterna kan lagras och bearbetas på samma chip.

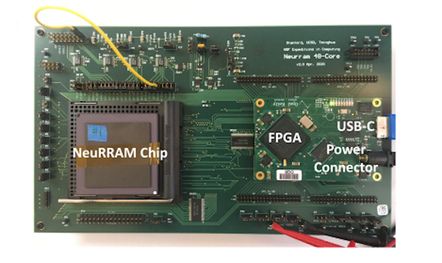

Ett compute-in-memory-chip baserat på resistivt slumpmässigt åtkomstminne (klicka för att förstora). Bild: Wan et al

Forskare bakom designen hävdar att det skulle vara mer effektivt för edge-applikationer eftersom det eliminerar datarörelse mellan separata beräknings- och minnesblock.

Edge computing och artificiell intelligens är båda på väg för meteorisk tillväxt inom en snar framtid, åtminstone enligt analytikerföretaget IDC. Vissa scenarier kombinerar dem eftersom edge-distributioner kan begränsas av ström och anslutning, men ändå måste analysera betydande datavolymer och leverera ett nästan realtidssvar på händelser, vilket gör en AI-modell som "bor" i enheten till den mest optimala lösningen .

I ljuset av detta har en grupp forskare utvecklat ett chip som det kallar NeuRRAM, eftersom det kombinerar artificiella neuroner med RRAM i en ny arkitektur. Målet med projektet var att leverera en design som samtidigt kan leverera hög energieffektivitet samt mångsidigheten för att stödja olika AI-modeller, och jämförbar noggrannhet med att köra samma modell i mjukvara.

Projektet startade ursprungligen som en del av ett Nature Science Foundation-projekt kallat "Expeditions in Computing". Detta projekt samlade en grupp forskare från olika institutioner med olika bakgrund, inklusive några från Stanford och UCSD, samt forskare vid Tsinghua University i Kina som är experter på tillverkning av RRAM-enheter.

Energieffektivitet: AI slutledning gjord på den batteridrivna prylen

Enligt Weier Wan, en forskare vid Stanford University och en av de tidningens författare, publicerad i Nature igår, har NeuRRAM utvecklats som ett AI-chip som avsevärt förbättrar energieffektiviteten för AI-inferens, vilket gör att komplexa AI-funktioner kan realiseras direkt i batteridrivna kantenheter, såsom smarta bärbara enheter, drönare och industriella IoT-sensorer .

"I dagens AI-chip sker databehandling och datalagring på separata platser – datorenhet och minnesenhet. Den frekventa datarörelsen mellan dessa enheter förbrukar mest energi och blir flaskhalsen för att förverkliga lågeffekts AI-processorer för avancerade enheter”, sa han.

För att ta itu med detta implementerar NeuRRAM-chippet en "compute-in-memory"-modell, där bearbetning sker direkt i minnet. Den använder också resistivt RAM (RRAM), en minnestyp som är lika snabb som statisk RAM men är icke-flyktig, vilket gör att den kan lagra AI-modellvikter. En nyckelfunktion hos RRAM-celler är att neurala vikter kan lagras i minnesceller som olika konduktansnivåer, kodas via digital-till-analog-omvandlare (DAC) och matas till minnesmatrisen.

Det här är ingen mjukvarusimulering, det är hårdvara

Det har gjorts tidigare studier på CIM-arkitekturer, men detta är den första som visar ett brett utbud av AI-applikationer i hårdvara snarare än i mjukvarusimulering, samtidigt som det är mer energieffektivt och kan köra algoritmerna exakt, något som ingen av de tidigare studierna har gjort. kunde visa samtidigt, enligt Wan.

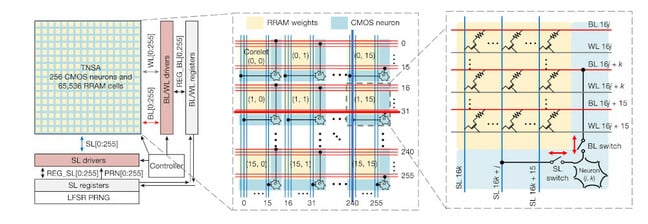

NeuRRAM består av 48 CIM-kärnor som består av totalt 3 miljoner RRAM-celler. Varje kärna beskrivs som en transposerbar neurosynaptisk array (TNSA) bestående av ett rutnät med 256 × 256 RRAM-celler och 256 CMOS artificiella neuronkretsar som implementerar analog-till-digital-omvandlare (ADC) och aktiveringsfunktioner.

Enligt tidningen har TNSA-arkitekturen utformats för att erbjuda flexibel kontroll av dataflödenas riktning, vilket är avgörande för att stödja ett brett utbud av AI-modeller med olika dataflödesmönster.

Till exempel, i konvolutionella neurala nätverk (CNN) som är vanliga i synrelaterade uppgifter, flödar data i en enda riktning genom lager för att generera datarepresentationer på olika abstraktionsnivåer, medan i vissa andra modeller utförs probabilistisk sampling fram och tillbaka mellan lagren tills nätverket konvergerar till ett tillstånd med hög sannolikhet.

Men andra konstruktioner som har kombinerat CIM med RRAM var begränsade till att arbeta i en enda riktning, vanligtvis genom att koppla rader och kolumner i RRAM-tvärstångsarrayen till dedikerade kretsar i periferin för att driva ingångar och mäta utgångar, säger tidningen.

Hur det fungerar

Hemligheten med NeuRRAM:s omkonfigurerbarhet är att den fördelar CMOS-neuronkretsarna mellan RRAM-cellerna och förbinder dem längs längden av både rader och kolumner.

Varje TNSA är uppdelad i ett antal corelets, som var och en består av 16 × 16 RRAM-celler och en neuronkrets. Corlets är förbundna med delade bitlinjer (BL) och ordlinjer (WLs) längs den horisontella riktningen och källlinjer (SLs) längs den vertikala riktningen.

Neuronkretsen ansluter via switchar till en BL och en SL av de 16 av varje som passerar genom coreleten, och är ansvarig för att integrera ingångar från alla 256 RRAM som ansluter till samma BL eller SL.

Varje neuronkrets kan använda sina BL- och SL-omkopplare för in- och utmatning. Detta innebär att den kan ta emot den analoga matris-vektormultiplikationen (MVM) från en RRAM-cell som kommer från antingen BL eller SL genom switcharna, men kan också skicka de konverterade digitala resultaten till perifera register via samma switchar.

Detta arrangemang innebär att olika dataflödesriktningar kan implementeras genom att konfigurera vilken switch som ska användas under ingångs- och utgångsstegen för varje neuronkrets.

(Denna arkitektur sätter oss också i åtanke något av SambaNovas AI-processorchip, som är implementerat som ett rutnät av beräkningsenheter och minnesenheter, länkade av en on-chip kommunikationsstruktur som styr dataflödet.)

För att maximera AI-inferensprestanda med de 48 CIM-kärnorna i NeuRRAM är det möjligt att implementera olika viktkartläggningsstrategier som utnyttjar både modellparallellism och dataparallellism, enligt tidningen.

I fallet med en CNN kan strategin vara att duplicera vikterna av de tidiga, mest beräkningsintensiva lagren till flera CIM-kärnor för parallell slutledning. Uppsatsen ger en mer detaljerad beskrivning av de tillgängliga viktkartläggningsstrategierna.

Tidningen rapporterar maskinvaruuppmätta slutledningsresultat med hjälp av chipet för en rad AI-uppgifter, inklusive bildklassificeringar med CIFAR-10 och MNIST-datauppsättningar, Googles talkommandoigenkänning och MNIST-bildåterställning, implementerad med olika AI-modeller.

Det påstås uppnå slutledningsnoggrannhet jämförbar med mjukvarumodeller som tränats med 4-bitars vikter för alla dessa benchmarkuppgifter. Till exempel uppnår den en felfrekvens på 0.98 procent på MNIST handskriven siffror igenkänning med en 7-lagers CNN, en 14.34 procent felfrekvens på CIFAR-10 objektklassificering med ResNet-20 och en 15.34 procent felfrekvens på Googles talkommando igenkänning med hjälp av en 4-cells LSTM (långt korttidsminne).

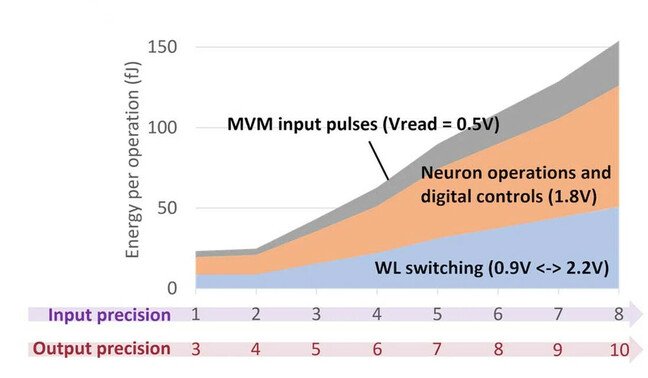

NeuRRAM-chippet påstås också ha en energieffektivitet som är två gånger bättre än tidigare CIM-chipdesigner som använder RRAM, över olika beräkningsbitprecisions. Energiförbrukningen i papperet anges dock inte i en form som är lätt att jämföra med kommersiella enheter på marknaden, och figuren nedan illustrerar energiförbrukningen per operation i olika bitprecision mätt i femtojoule (fJ).

Men Wan berättade för oss att för en typisk sökordsupptäckningsuppgift i realtid som körs på många smarta hemenheter idag (som att säga åt en smart högtalare att tända ljuset), beräknas NeuRRAM förbruka mindre än 2 mikrowatt ström.

"Det betyder att även på ett litet myntbatteri kan det fungera i mer än 10 år (utan hänsyn till ström som förbrukas av andra systemkomponenter)", sa han.

Enligt tidningen är chipet tillverkat med en 130nm CMOS-teknik, och det förväntas att energieffektiviteten förbättras med teknologiska skalningen, vilket är fallet för andra halvledarprodukter.

Produktisering fortfarande år bort

Så kommer vi att se en kommersiell utrustning baserad på denna teknik? Wan säger att det har stor potential att kommersialiseras och funderar personligen på att själv produktisera det.

"Det mest lämpliga initiala användningsfallet är mycket troligt i extrem edge / IoT," berättade han för oss.

En produkt baserad på NeuRRAM-chippet skulle kunna kombineras i ett system med en CPU, som med andra acceleratorer, men detta är inte nödvändigt för alla applikationer.

"Nyligen har det funnits en trend att data från sensorer matas direkt till AI-processorer utan att gå igenom CPU eller extra minne," sa Wan, men han tillade att för de flesta fall i verkligheten fungerar sådana AI-acceleratorer som en co-processor för en CPU, där CPU:n hanterar andra uppgifter.

NeuRRAM-chippet är endast avsett för slutledningsarbete, till stor del för att RRAM-tekniken i sin nuvarande form inte är särskilt lämplig för träning eftersom träningsprocessen kräver frekventa uppdateringar av minnet, och detta är "en mycket dyr operation på RRAM" sa Wan.

"För närvarande har många kommersiella gjuterier redan kapaciteten att tillverka RRAM-enheter, men mest för användning av inbyggt minne snarare än för compute-in-memory. När RRAM-processen blir mer allmänt tillgänglig för IC-designers, kan en NeuRRAM-produkt hända."

Den exakta tidslinjen för att detta ska hända är dock svår att förutsäga, och Wan sa att det kan vara inom de kommande två till tre åren, eller mycket längre. ®

- AI

- ai konst

- ai art generator

- har robot

- artificiell intelligens

- artificiell intelligenscertifiering

- artificiell intelligens inom bankväsendet

- artificiell intelligens robot

- robotar med artificiell intelligens

- programvara för artificiell intelligens

- blockchain

- blockchain konferens ai

- coingenius

- konversationskonstnärlig intelligens

- kryptokonferens ai

- dalls

- djupt lärande

- du har google

- maskininlärning

- plato

- plato ai

- Platon Data Intelligence

- Platon spel

- PlatonData

- platogaming

- skala ai

- syntax

- Registret

- zephyrnet